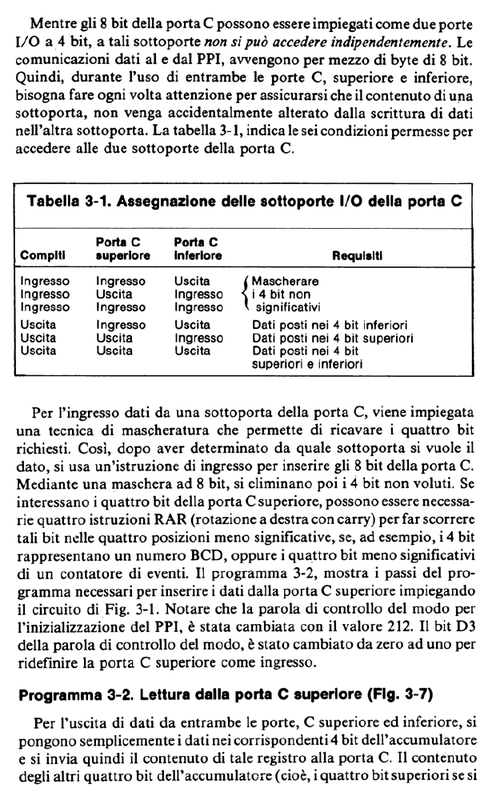

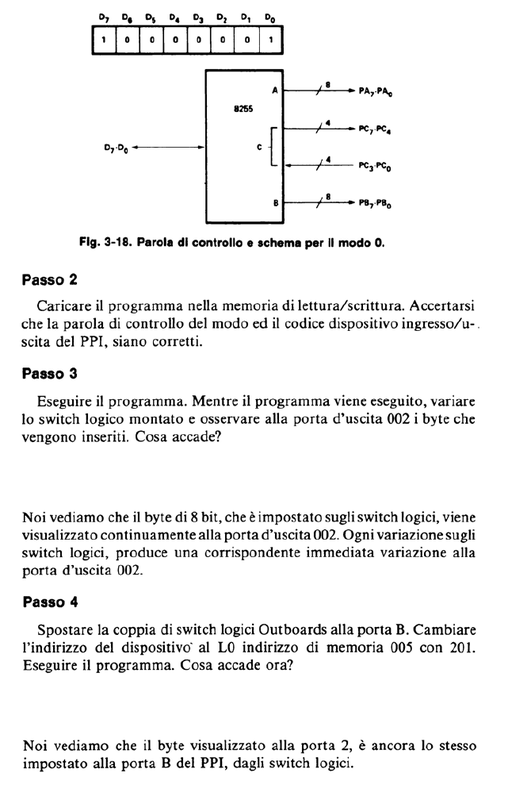

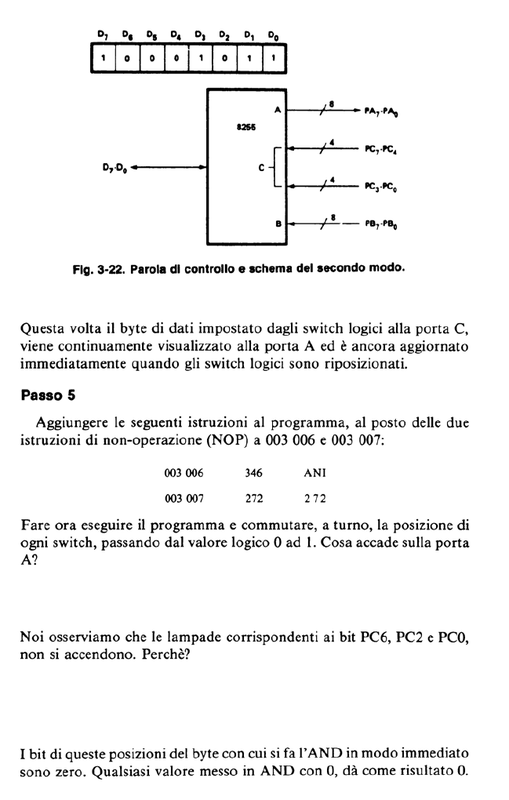

Lo Z80 nanocomputer

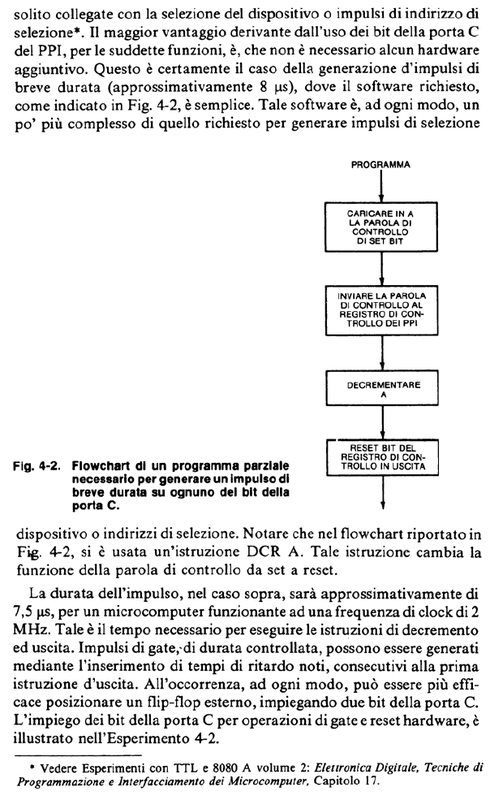

elementare

Mi rendo conto dell'anacronismo con cui presento il seguente obsoleto lavoro: lo Z80.

A ridosso dei nostri tempi, fa certo ridere un microcomputer degno degli albori dell'informatica; colui che non ride è, come me, lo sperimentatore di cose già fatte.

Così potremmo definirci noi dilettanti in elettronica: sperimentatori non solo di cose già fatte, ma anche ampiamente funzionanti, senza il nostro contributo.

Pertanto quanto noi facciamo non è di alcuna utilità, ma è solo per nostro divertimento, come direbbero gli Inglesi: un Gadget.

Allora se lo scopo è divertirsi, possiamo accettare di buon grado anche questo progetto, come accettiamo di buon grado di usare la bicicletta, velocipede del periodo storico egiziano di età faraonica.

Considerate questo progetto un po' come un "Arduino" casareccio, il quale, nel prosieguo, potrete ampliare secondo i numerosi altri schemi complementari che andrò, man mano, fornendovi.

Lo Z80 è un microprocessore che costituisce l'evoluzione dell'8080 degli anni '60-'70, a sua volta, evoluzione del 4004, progettato e costruito come "meccanismo" per i primi orologi digitali.

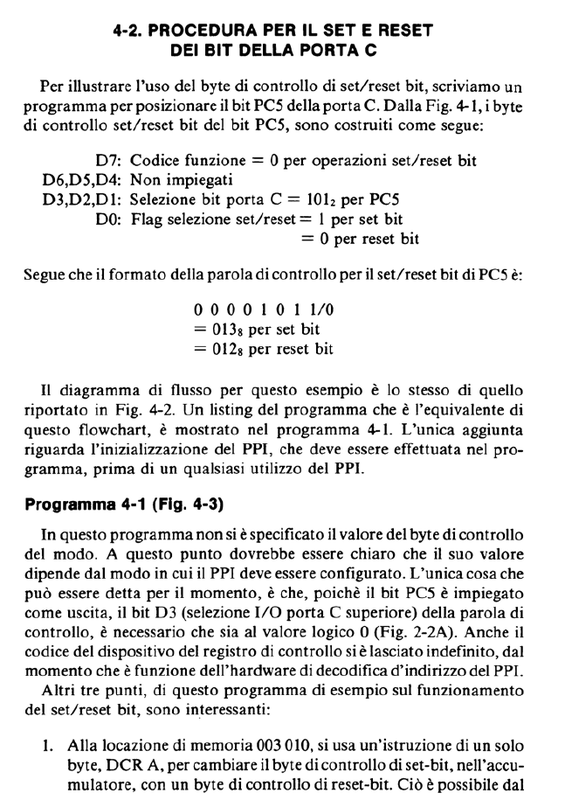

Esso è il padre del 6800 e del 9008, a tutt'ora base dei microprocessori odierni.

L'altro filone è quello del 6502 che aveva dato origine al micromputer Commodore, mentre lo Z80 era stato il cuore dello Spectrum.

L'Apple ha sempre seguito una strada molto più aristocratica, professionale e meno divulgativa.

So che moltissimi di voi conservano ancora gelosamente lo Spectrum o il Commodore.

L'insieme dei comandi dello Z80 consta di 256 codici operativi o istruzioni in linguaggio macchina, cui seguirà il linguaggio mnemonico, l'Assembler , il Basic il Cobol, il Fortran, il Pascal, linguaggio C e tutti gli altri linguaggi più evoluti.

Il linguaggio macchina è formato da sequenza di simboli che sono una combinazione di zero e uno secondo le potenze di due.

Esso è il sistema di munerazione posizionale più primitivo, retrogrado ed inefficiente che possa esistere, ma il più facilmente realizzabile in elettronica: tutto o niente; acceso o spento; tensione zero o tensione di alimentazione; livello alto H, livello basso L.

l sistema di numerazione decimale esprime il numero 1000 con quattro cifre, il sistema binario ne richiede dieci.

Tuttavia è stato adottato universalmente grazie all'alta, al giorno d'oggi altissima, velocità di esecuzione, che consente di ovviare a questa gravissima inefficienza.

Non mi dilungo oltre perché è nei miei scopi rivolgermi a persone che conoscano le logiche digitali, le porte logiche e le loro combinazioni circuitali, le tavole della verità in mancanza dell'algebra Booleana, i contatori binari, il sistema di numerazione binario (il linguaggio in ottale ed esadecimale) e chi più ne ha più ne metta.

Pertanto do per scontato anche la conoscenza, almeno di base, dei microprocessori 8080 e Z80.

Per chi volesse saperne di più o mettersi al passo o addirittura iniziare, fornisco l'indirizzo (su questo stesso sito) dove trovare le principali pubblicazioni divulgative a riguardo, in lingua italiana.

http://isoondaomradio.weebly.com/8080-e-z80-i-nanocomputers.html

Per chi ha bisogno di una sola rinfrescata continui pure la lettura.

Perché in fondo si tratta di assaporare o di riassaporare questo "diverso" tipo di elettronica: rigidamente esatta, necessaria e sufficiente, che costringe ad alte attenzioni e non concede errori; insomma non c'è via di mezzo, non è che la cosa funzionicchia, o funziona o non funziona.

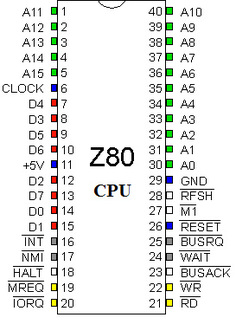

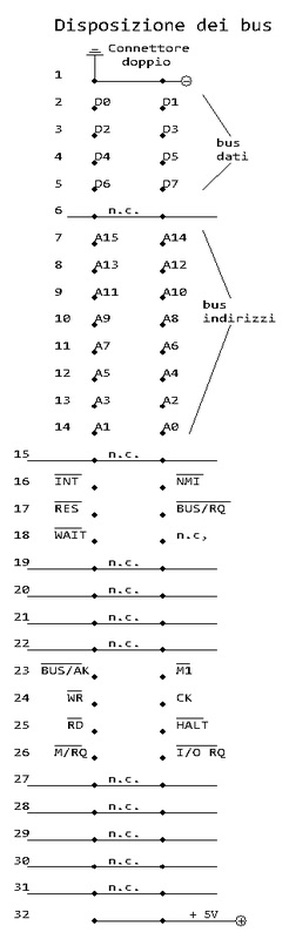

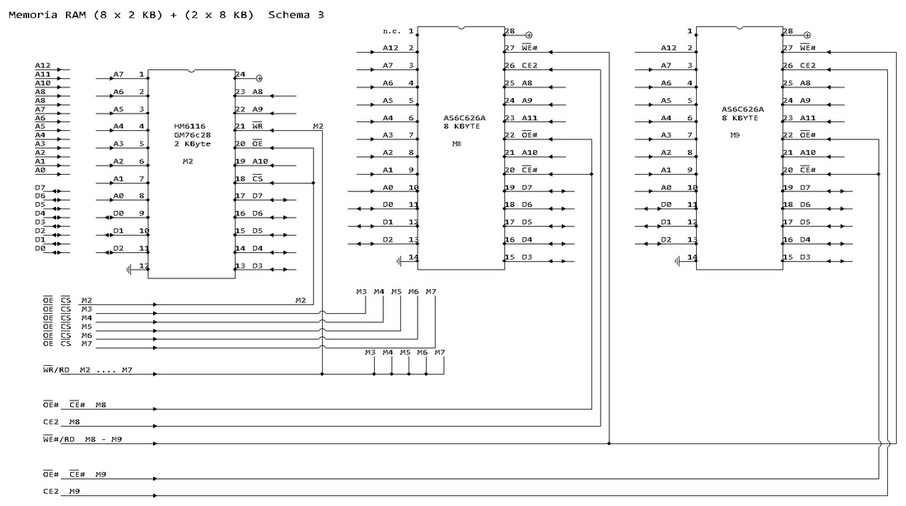

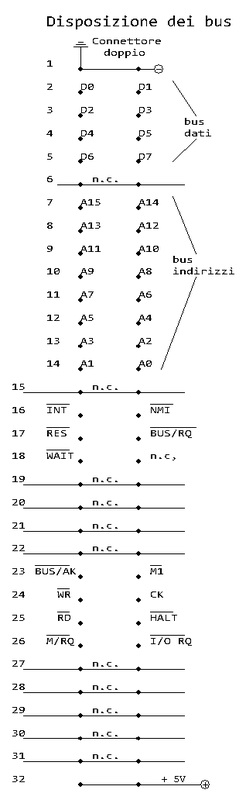

Lo Z80 possiede tre tipi di "bus" ossia gruppi linee multifilari di comunicazione:

un bus indirizzi di 16 bit (unità elementare in binario), gestito dal contatore di programma o settabile manualmente;

un bus di dati 8 bit bidirezionale;

un bus comandi di 13 bit;

un pin di clock e due di alimentazione.

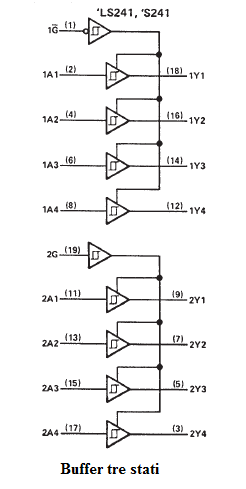

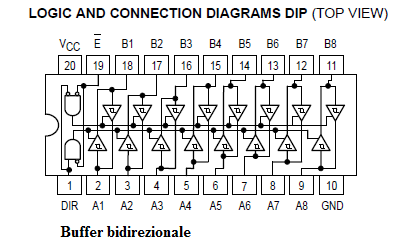

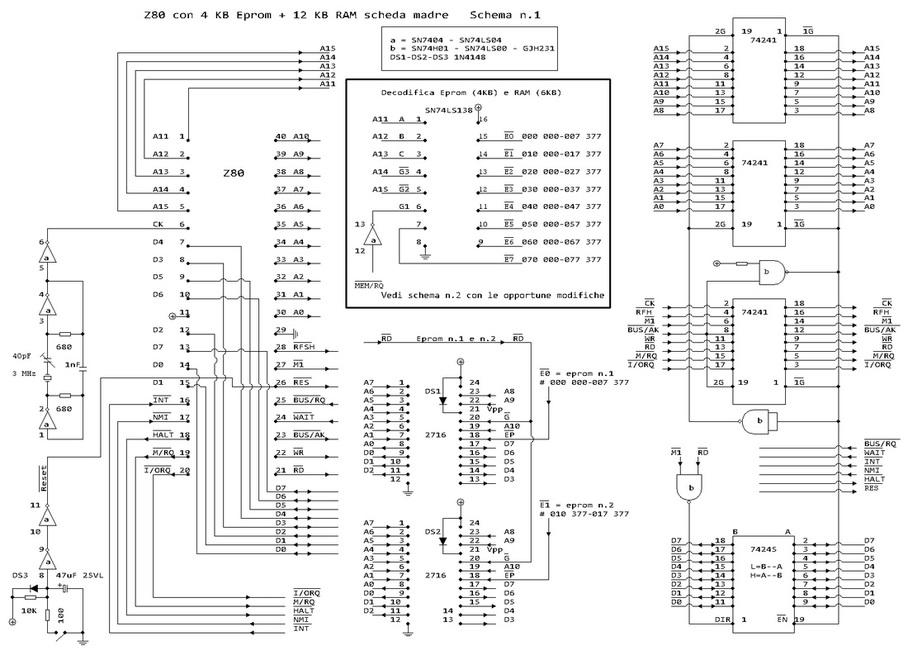

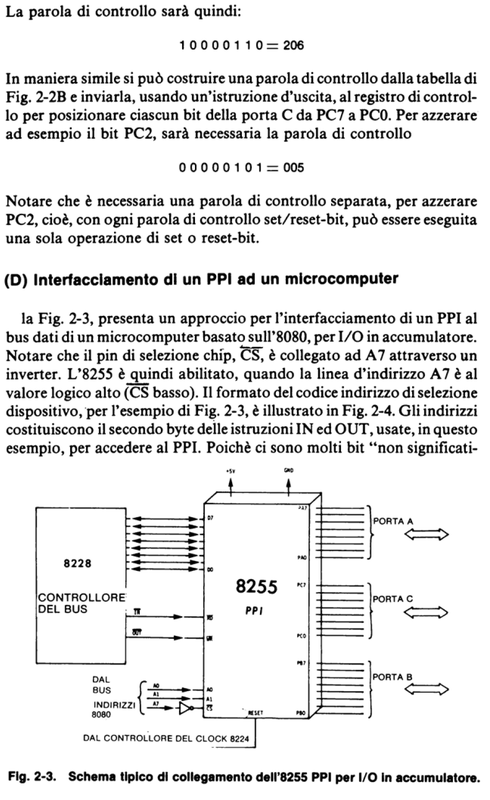

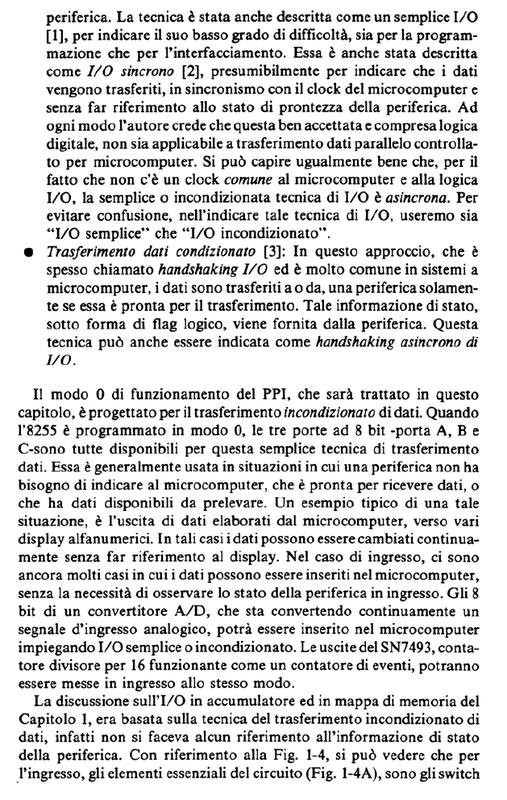

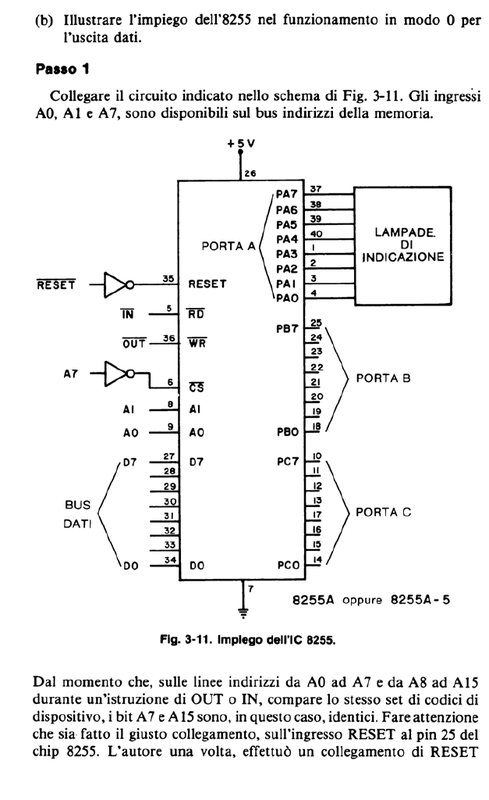

Il sistema proposto consta di una scheda madre con il processore, l'oscillatore ad onda quadra per pilotare lo Z80, il sistema di azzeramento (reset), due banchi di memorie e gli amplificatori di segnali "buffer" e tre stati, figura n. 1, i circuiti asserviti sono tutti TTL o compatibili TTL con alimentazione a 5V.

A ridosso dei nostri tempi, fa certo ridere un microcomputer degno degli albori dell'informatica; colui che non ride è, come me, lo sperimentatore di cose già fatte.

Così potremmo definirci noi dilettanti in elettronica: sperimentatori non solo di cose già fatte, ma anche ampiamente funzionanti, senza il nostro contributo.

Pertanto quanto noi facciamo non è di alcuna utilità, ma è solo per nostro divertimento, come direbbero gli Inglesi: un Gadget.

Allora se lo scopo è divertirsi, possiamo accettare di buon grado anche questo progetto, come accettiamo di buon grado di usare la bicicletta, velocipede del periodo storico egiziano di età faraonica.

Considerate questo progetto un po' come un "Arduino" casareccio, il quale, nel prosieguo, potrete ampliare secondo i numerosi altri schemi complementari che andrò, man mano, fornendovi.

Lo Z80 è un microprocessore che costituisce l'evoluzione dell'8080 degli anni '60-'70, a sua volta, evoluzione del 4004, progettato e costruito come "meccanismo" per i primi orologi digitali.

Esso è il padre del 6800 e del 9008, a tutt'ora base dei microprocessori odierni.

L'altro filone è quello del 6502 che aveva dato origine al micromputer Commodore, mentre lo Z80 era stato il cuore dello Spectrum.

L'Apple ha sempre seguito una strada molto più aristocratica, professionale e meno divulgativa.

So che moltissimi di voi conservano ancora gelosamente lo Spectrum o il Commodore.

L'insieme dei comandi dello Z80 consta di 256 codici operativi o istruzioni in linguaggio macchina, cui seguirà il linguaggio mnemonico, l'Assembler , il Basic il Cobol, il Fortran, il Pascal, linguaggio C e tutti gli altri linguaggi più evoluti.

Il linguaggio macchina è formato da sequenza di simboli che sono una combinazione di zero e uno secondo le potenze di due.

Esso è il sistema di munerazione posizionale più primitivo, retrogrado ed inefficiente che possa esistere, ma il più facilmente realizzabile in elettronica: tutto o niente; acceso o spento; tensione zero o tensione di alimentazione; livello alto H, livello basso L.

l sistema di numerazione decimale esprime il numero 1000 con quattro cifre, il sistema binario ne richiede dieci.

Tuttavia è stato adottato universalmente grazie all'alta, al giorno d'oggi altissima, velocità di esecuzione, che consente di ovviare a questa gravissima inefficienza.

Non mi dilungo oltre perché è nei miei scopi rivolgermi a persone che conoscano le logiche digitali, le porte logiche e le loro combinazioni circuitali, le tavole della verità in mancanza dell'algebra Booleana, i contatori binari, il sistema di numerazione binario (il linguaggio in ottale ed esadecimale) e chi più ne ha più ne metta.

Pertanto do per scontato anche la conoscenza, almeno di base, dei microprocessori 8080 e Z80.

Per chi volesse saperne di più o mettersi al passo o addirittura iniziare, fornisco l'indirizzo (su questo stesso sito) dove trovare le principali pubblicazioni divulgative a riguardo, in lingua italiana.

http://isoondaomradio.weebly.com/8080-e-z80-i-nanocomputers.html

Per chi ha bisogno di una sola rinfrescata continui pure la lettura.

Perché in fondo si tratta di assaporare o di riassaporare questo "diverso" tipo di elettronica: rigidamente esatta, necessaria e sufficiente, che costringe ad alte attenzioni e non concede errori; insomma non c'è via di mezzo, non è che la cosa funzionicchia, o funziona o non funziona.

Lo Z80 possiede tre tipi di "bus" ossia gruppi linee multifilari di comunicazione:

un bus indirizzi di 16 bit (unità elementare in binario), gestito dal contatore di programma o settabile manualmente;

un bus di dati 8 bit bidirezionale;

un bus comandi di 13 bit;

un pin di clock e due di alimentazione.

Il sistema proposto consta di una scheda madre con il processore, l'oscillatore ad onda quadra per pilotare lo Z80, il sistema di azzeramento (reset), due banchi di memorie e gli amplificatori di segnali "buffer" e tre stati, figura n. 1, i circuiti asserviti sono tutti TTL o compatibili TTL con alimentazione a 5V.

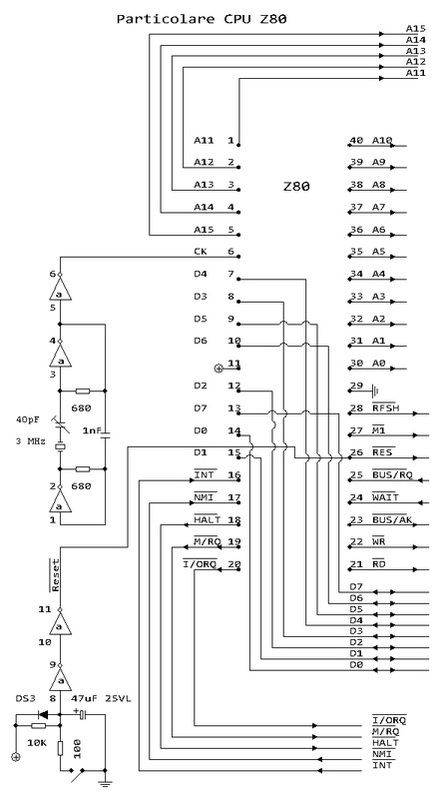

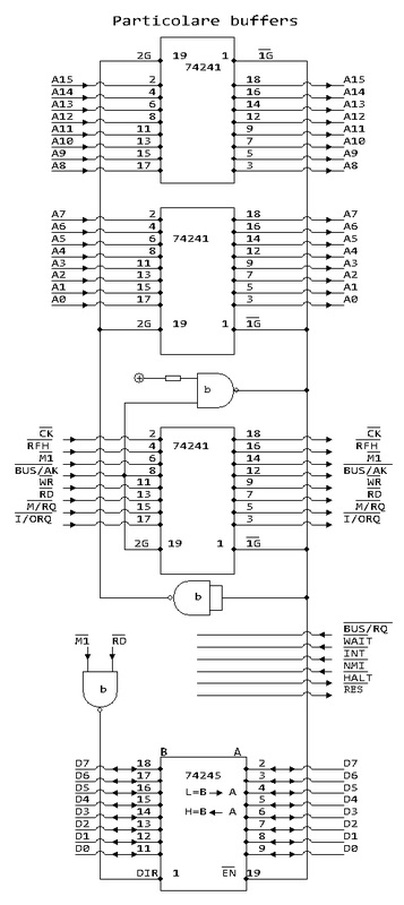

Poiché la corrente fornita dal "cip" Z80 è scarsa è necessario non sovraccaricarlo, onde necessita interporre tra la CPU e le periferiche i summenzionati buffer.

I buffer sono a tre stati perché sono in grado di comunicare il livello L il livello H ed

a porsi in stato di alta impedenza (inerte) qualora le periferiche debbano essere controllata da altre funzioni, che la CPU non svolge personalmente. Questo avverrà attraverso l'attivazione della linea di comando, in ingresso, BUS REQUEST (BUS/RQ), cui la CPU risponde con l'attivazione (livello L) della linea, in uscita, BUS/ACKNOWLEDGE (BUS/AK).

Il buffer dati trasferisce il segnale inalterato, ma con disponibilità molto maggiore di corrente,

è bidirezionale perché sullo stesso bus possano transitare dati nei due versi: in uscita ed in entrata.

Gli altri buffer sono solo unidirezionali: dalla CPU verso le periferiche, con possibilità di porsi, a loro volta, in alta impedenza (Hi Z).

I buffer sono a tre stati perché sono in grado di comunicare il livello L il livello H ed

a porsi in stato di alta impedenza (inerte) qualora le periferiche debbano essere controllata da altre funzioni, che la CPU non svolge personalmente. Questo avverrà attraverso l'attivazione della linea di comando, in ingresso, BUS REQUEST (BUS/RQ), cui la CPU risponde con l'attivazione (livello L) della linea, in uscita, BUS/ACKNOWLEDGE (BUS/AK).

Il buffer dati trasferisce il segnale inalterato, ma con disponibilità molto maggiore di corrente,

è bidirezionale perché sullo stesso bus possano transitare dati nei due versi: in uscita ed in entrata.

Gli altri buffer sono solo unidirezionali: dalla CPU verso le periferiche, con possibilità di porsi, a loro volta, in alta impedenza (Hi Z).

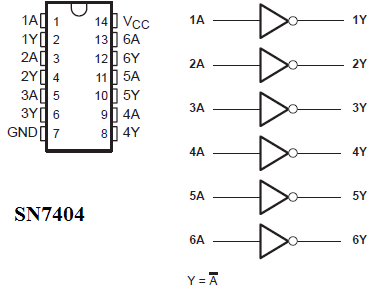

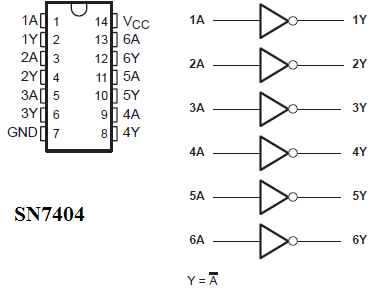

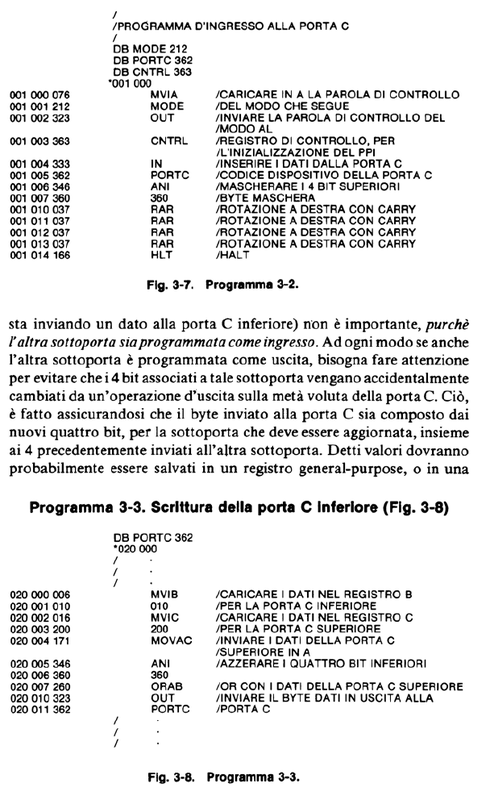

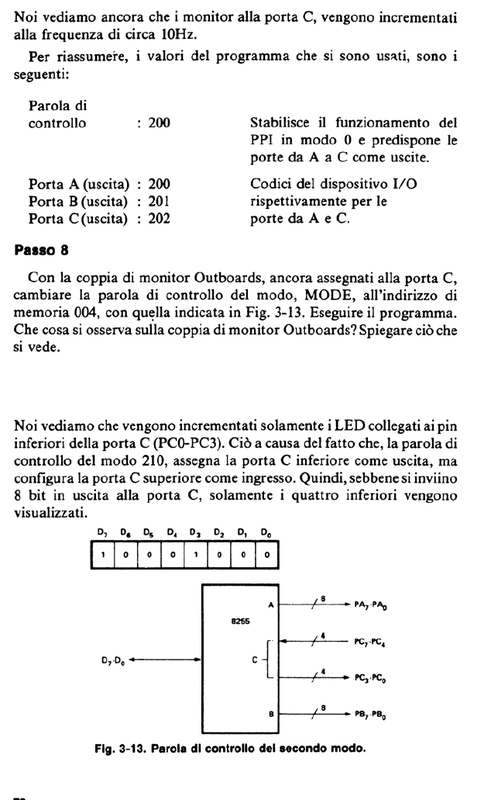

Schema n. 1: il segnale di azzeramento (reset) viene fornito da due porte NOT (SN7404); il segnale di clock viene fornito da tre porte invertenti NOT (SN7404) che fanno oscillare, in onda quadra, un quarzo da tre MHz.

Il tipo di CPU Z80 che io monto sarebbe anche capace di arrivare fino ad un clock di quattro MHz, ma le 7216 (Eprom abbastanza lente) non reggerebbero questa frequenza ed i dati transiterebbero con moltissimi errori.

Se usate le 2716 badate ai modelli perché hanno tempi di propagazione diversi, ma ben difficilmente scenderete sotto i 300-350 nSec.

Allora è inutile acquistare gli ultimi modelle di Z80 funzionanti fino a 10 MHz, se poi usate delle 21716, a meno che non vi siate costretti.

Ho raggruppato graficamente i bus in gruppi ordinati crescenti dal basso verso l'alto.

Ho solo indicati i collegamenti reciproci con denominazioni uguali che, naturalmente, andranno connessi gli uni con gli altri.

Per una maggiore comprensione, fornisco anche una visione d'insieme e di principio della scheda madre in figura 1.

C'è da dire che, a seconda dei modelli di Z80, sono disponibili correnti diverse ai singoli piedini, questo comporta alcune distinzioni circa il numero delle unità di memoria, direttamente collegabile alla CPU. Nei modelli più antichi (cip ad 1 MHz) è consigliabile non superare il numero di due banchi di memoria e dirigersi subito ai buffer (SN74241 e SN74245) elevatori di corrente, in modo da poter o pilotare le altre memorie e le periferiche. Nei modelli da 3-4 MHz in su si può giungere a 4 banchi di memoria.

Il tipo di CPU Z80 che io monto sarebbe anche capace di arrivare fino ad un clock di quattro MHz, ma le 7216 (Eprom abbastanza lente) non reggerebbero questa frequenza ed i dati transiterebbero con moltissimi errori.

Se usate le 2716 badate ai modelli perché hanno tempi di propagazione diversi, ma ben difficilmente scenderete sotto i 300-350 nSec.

Allora è inutile acquistare gli ultimi modelle di Z80 funzionanti fino a 10 MHz, se poi usate delle 21716, a meno che non vi siate costretti.

Ho raggruppato graficamente i bus in gruppi ordinati crescenti dal basso verso l'alto.

Ho solo indicati i collegamenti reciproci con denominazioni uguali che, naturalmente, andranno connessi gli uni con gli altri.

Per una maggiore comprensione, fornisco anche una visione d'insieme e di principio della scheda madre in figura 1.

C'è da dire che, a seconda dei modelli di Z80, sono disponibili correnti diverse ai singoli piedini, questo comporta alcune distinzioni circa il numero delle unità di memoria, direttamente collegabile alla CPU. Nei modelli più antichi (cip ad 1 MHz) è consigliabile non superare il numero di due banchi di memoria e dirigersi subito ai buffer (SN74241 e SN74245) elevatori di corrente, in modo da poter o pilotare le altre memorie e le periferiche. Nei modelli da 3-4 MHz in su si può giungere a 4 banchi di memoria.

Naturalmente ciò è anche funzione del tipo di memoria usata, cioè ad assorbimento di maggiore o minore corrente.

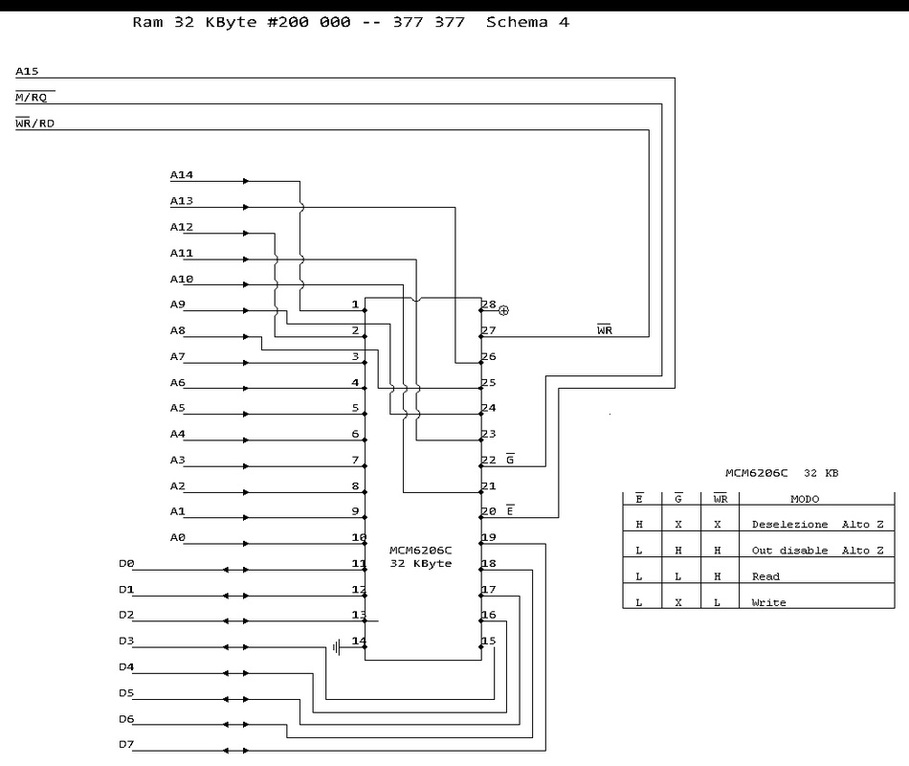

I tipi più antichi come le 2716 e le HM 6116 hanno assorbimenti relativamente alti, mentre i modelli più recenti come le AS6C626A (8 KB) e le MCM6206C (32kB) assorbono correnti modestissime, quindi sarebbero collegabili, in maggior numero, direttamente allo Z80.

I buffer restano comunque indispensabili anche perché svolgono la funzione di isolatori tra la scheda madre ed il resto del sistema.

Essi infatti, come già detto, possono essere posti in stato di alta impedenza come risposta al segnale ( livello L) di BUS/RQ (bus request = richiesta di bus), nel caso un processo indipendente chiedesse alla CPU di poter accedere ai contenuti delle memorie o di inviare dati alle memorie stesse o prendere il pilotaggio di qualche periferica gestita anche dalla CPU.

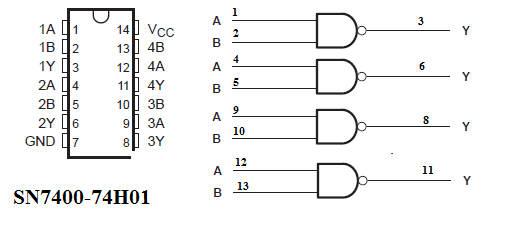

Come infatti noterete il piedino BUS/AK (bus acknowledge = riconoscimento di bus) dello Z80 pilota gli ingressi dei buffer che determinano lo stato ad alto Z dei cip, mentre i segnali M1 e RD, abbinati su di una porta NAND (SN7400, Sn74H01, GJH 231) , pilotano il verso di transito dei dati

M1 è un segnale (livello L) che viene emesso ogniqualvolta viene effettuato un accesso in memoria per il prelievo del codice operativo (Fetch) ed RD (livello L) è un segnale emesso se si tratta di lettura in memoria o su porta I/O.

MEM/RQ viene generato (livello L) quando si richiede un accesso alla memoria sia in lettura sia in scrittura.

Per operazioni di I/O diventano attivi (livello L) i segnali I/O RQ e RD per la lettuta, I/O RQ e WR per la scrittura.

Potrete trovare il dettaglio di ogni altra funzione, scaricando Il NanonbooK Z-80 vol. III a pag. 5 e seguenti.

http://isoondaomradio.weebly.com/8080-e-z80-i-nanocomputers.html

La scheda madre è quindi un insieme di circuiti il cui numero stabilirete voi stessi, attraverso le vostre esigenze ed i modelli di cip di cui disponete, io ve ne do, genericamente, una configurazione funzionante ad immagine e somiglianza del sistema che io uso.

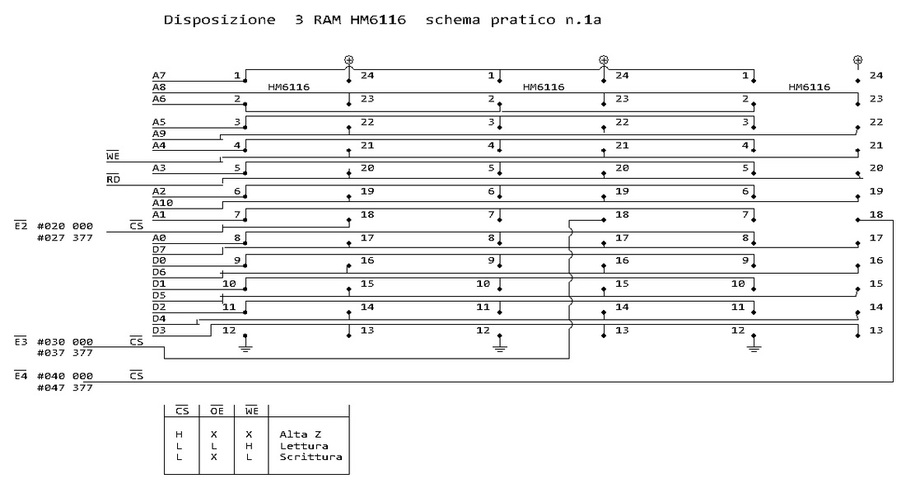

I collegamenti nello schema pratico n.1a vanno effettuati con apposito filo sottilissimo isolato per wire wrap.

I tipi più antichi come le 2716 e le HM 6116 hanno assorbimenti relativamente alti, mentre i modelli più recenti come le AS6C626A (8 KB) e le MCM6206C (32kB) assorbono correnti modestissime, quindi sarebbero collegabili, in maggior numero, direttamente allo Z80.

I buffer restano comunque indispensabili anche perché svolgono la funzione di isolatori tra la scheda madre ed il resto del sistema.

Essi infatti, come già detto, possono essere posti in stato di alta impedenza come risposta al segnale ( livello L) di BUS/RQ (bus request = richiesta di bus), nel caso un processo indipendente chiedesse alla CPU di poter accedere ai contenuti delle memorie o di inviare dati alle memorie stesse o prendere il pilotaggio di qualche periferica gestita anche dalla CPU.

Come infatti noterete il piedino BUS/AK (bus acknowledge = riconoscimento di bus) dello Z80 pilota gli ingressi dei buffer che determinano lo stato ad alto Z dei cip, mentre i segnali M1 e RD, abbinati su di una porta NAND (SN7400, Sn74H01, GJH 231) , pilotano il verso di transito dei dati

M1 è un segnale (livello L) che viene emesso ogniqualvolta viene effettuato un accesso in memoria per il prelievo del codice operativo (Fetch) ed RD (livello L) è un segnale emesso se si tratta di lettura in memoria o su porta I/O.

MEM/RQ viene generato (livello L) quando si richiede un accesso alla memoria sia in lettura sia in scrittura.

Per operazioni di I/O diventano attivi (livello L) i segnali I/O RQ e RD per la lettuta, I/O RQ e WR per la scrittura.

Potrete trovare il dettaglio di ogni altra funzione, scaricando Il NanonbooK Z-80 vol. III a pag. 5 e seguenti.

http://isoondaomradio.weebly.com/8080-e-z80-i-nanocomputers.html

La scheda madre è quindi un insieme di circuiti il cui numero stabilirete voi stessi, attraverso le vostre esigenze ed i modelli di cip di cui disponete, io ve ne do, genericamente, una configurazione funzionante ad immagine e somiglianza del sistema che io uso.

I collegamenti nello schema pratico n.1a vanno effettuati con apposito filo sottilissimo isolato per wire wrap.

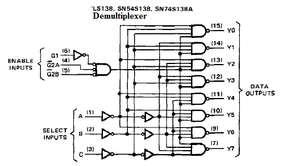

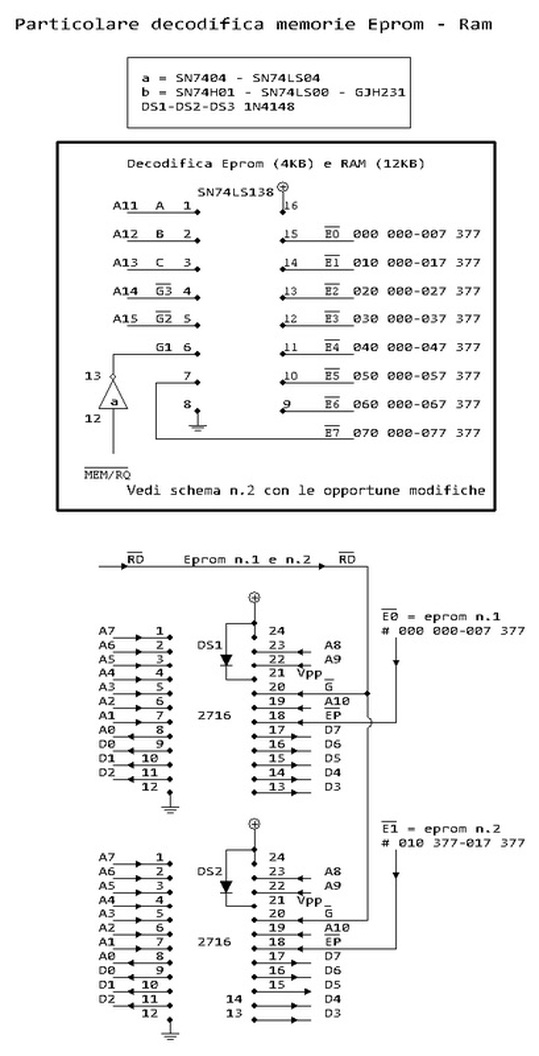

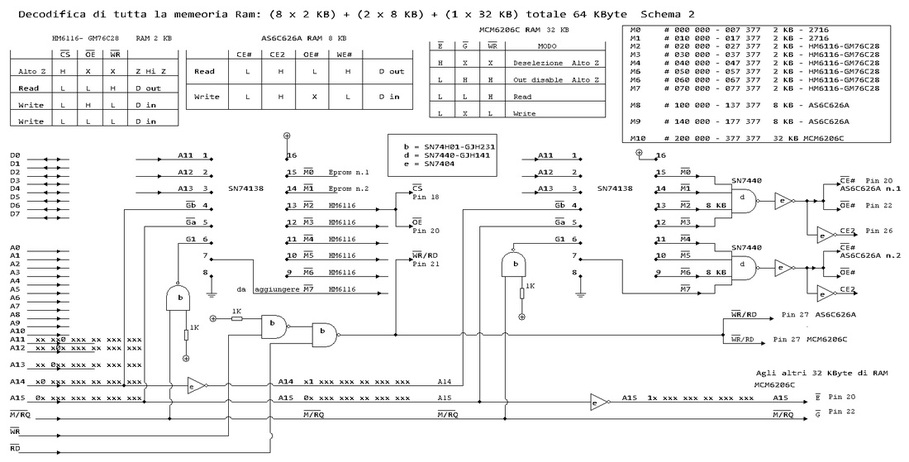

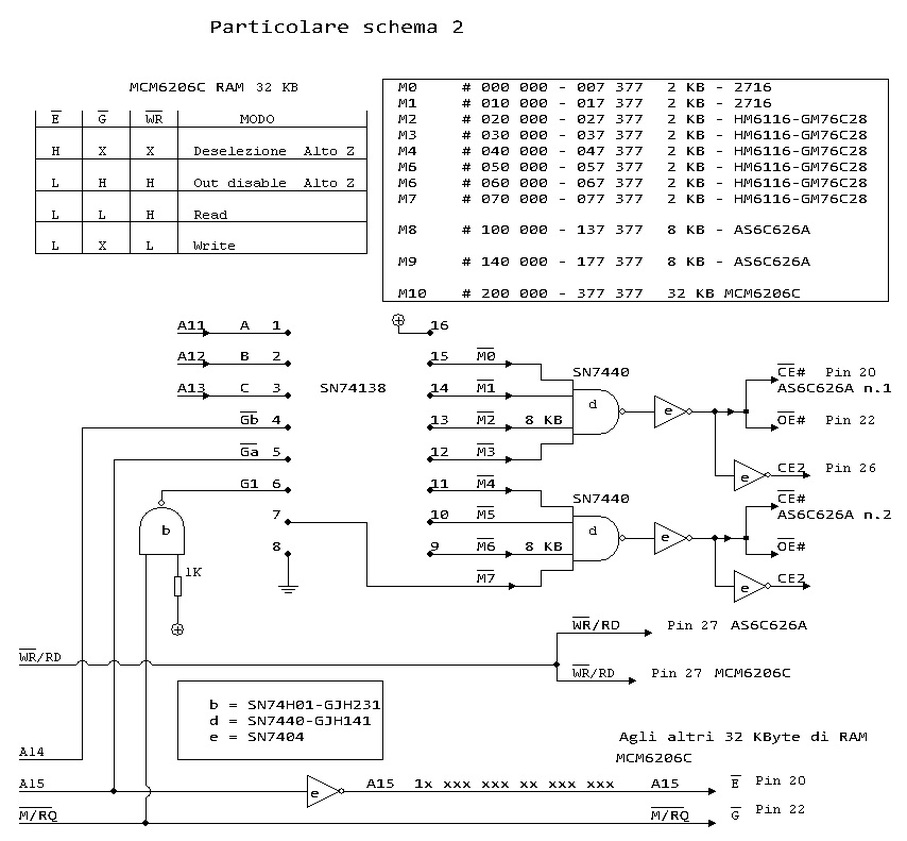

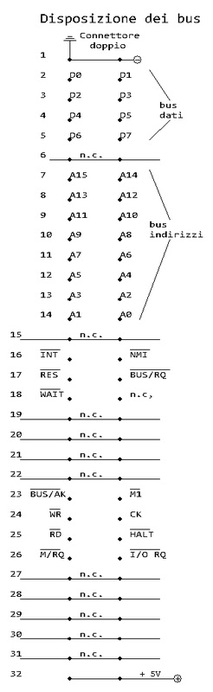

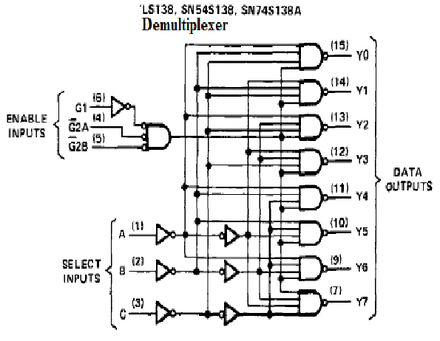

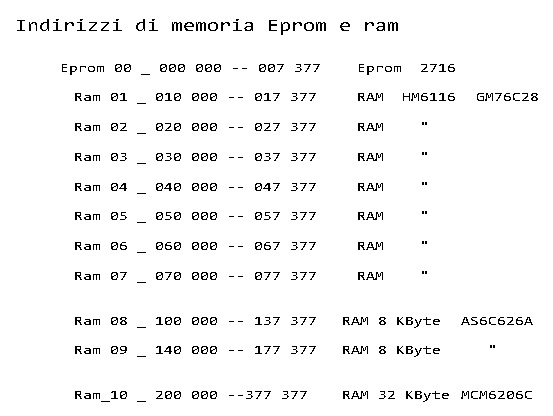

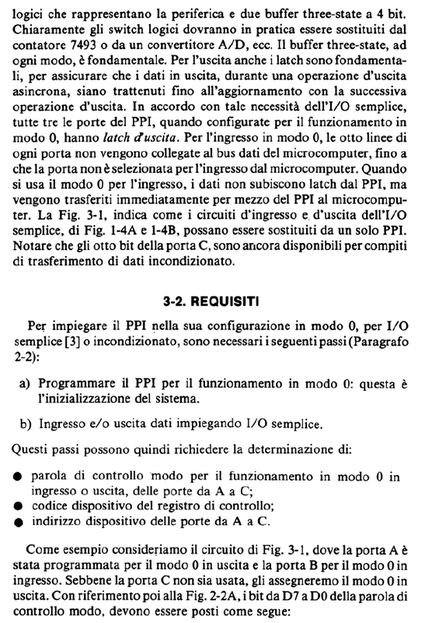

Lo schema n.2 tratta la logica circuitale per la decodifica univoca dei banchi di memoria; sono

previsti banchi di memoria di diversa capacità:

otto banchi da 2048 Byte (2 KB), due banchi da 8192 Byte (8 KB), un banco da 32768 Byte (32 KB) con un totale di 65536 (64 KB).

Da 2 a 16 KB di memoria (decodifica con il primo SN74138);

da 16 a 32 KB di memoria (decodifica con il secondo SN74138);

infine ampliamento da 32 a 64 KB di memoria.

Non vi sono particolari notevoli se non quello che, comunque sia, la decodifica resta univoca per qualsiasi quantità di memoria, cioè non vi sono ridondanze (ripetizioni) su altri indirizzi, qualsiasi essi siano.

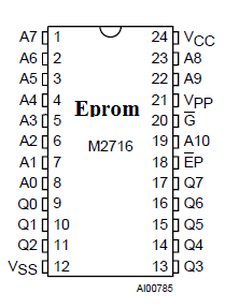

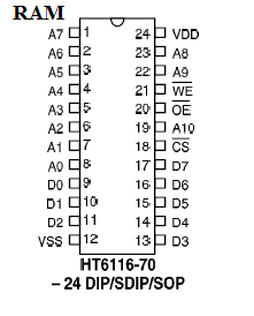

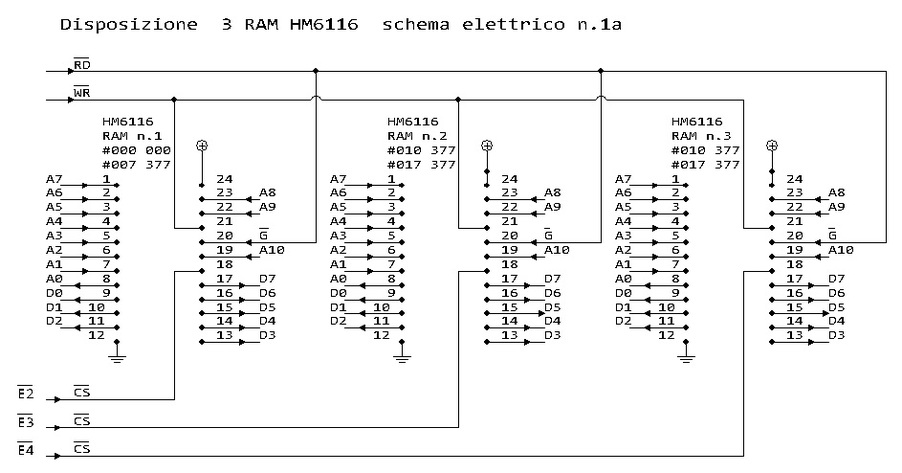

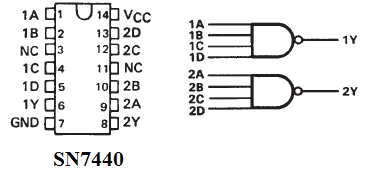

Gli otto banchi da 2 KB constano di una o due Eprom 2716 (memoria cancellabile a sola lettura) e sei RAM statiche (memorie ad accesso casuale) HM6116 o GM76C28 (vedi schemi n. 3), ma possono essere sostituite con altre (a minor consumo di corrente) apportando le debite variazioni ai collegamenti,.

I due banchi da 8 KB sono "implementati" da due AS6C626A con lo stesso discorso di cui sopra.

L'ultimo banco è da 32 KB: un MCM6206C

previsti banchi di memoria di diversa capacità:

otto banchi da 2048 Byte (2 KB), due banchi da 8192 Byte (8 KB), un banco da 32768 Byte (32 KB) con un totale di 65536 (64 KB).

Da 2 a 16 KB di memoria (decodifica con il primo SN74138);

da 16 a 32 KB di memoria (decodifica con il secondo SN74138);

infine ampliamento da 32 a 64 KB di memoria.

Non vi sono particolari notevoli se non quello che, comunque sia, la decodifica resta univoca per qualsiasi quantità di memoria, cioè non vi sono ridondanze (ripetizioni) su altri indirizzi, qualsiasi essi siano.

Gli otto banchi da 2 KB constano di una o due Eprom 2716 (memoria cancellabile a sola lettura) e sei RAM statiche (memorie ad accesso casuale) HM6116 o GM76C28 (vedi schemi n. 3), ma possono essere sostituite con altre (a minor consumo di corrente) apportando le debite variazioni ai collegamenti,.

I due banchi da 8 KB sono "implementati" da due AS6C626A con lo stesso discorso di cui sopra.

L'ultimo banco è da 32 KB: un MCM6206C

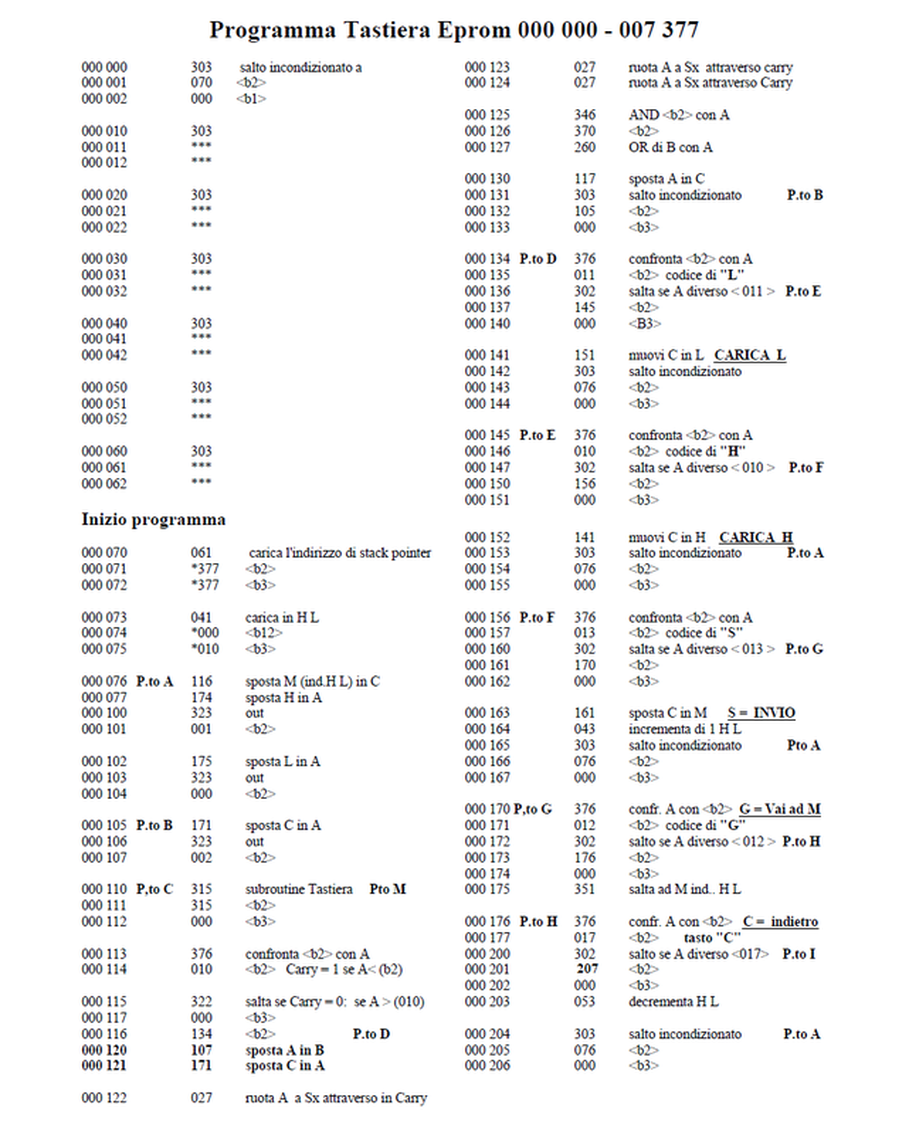

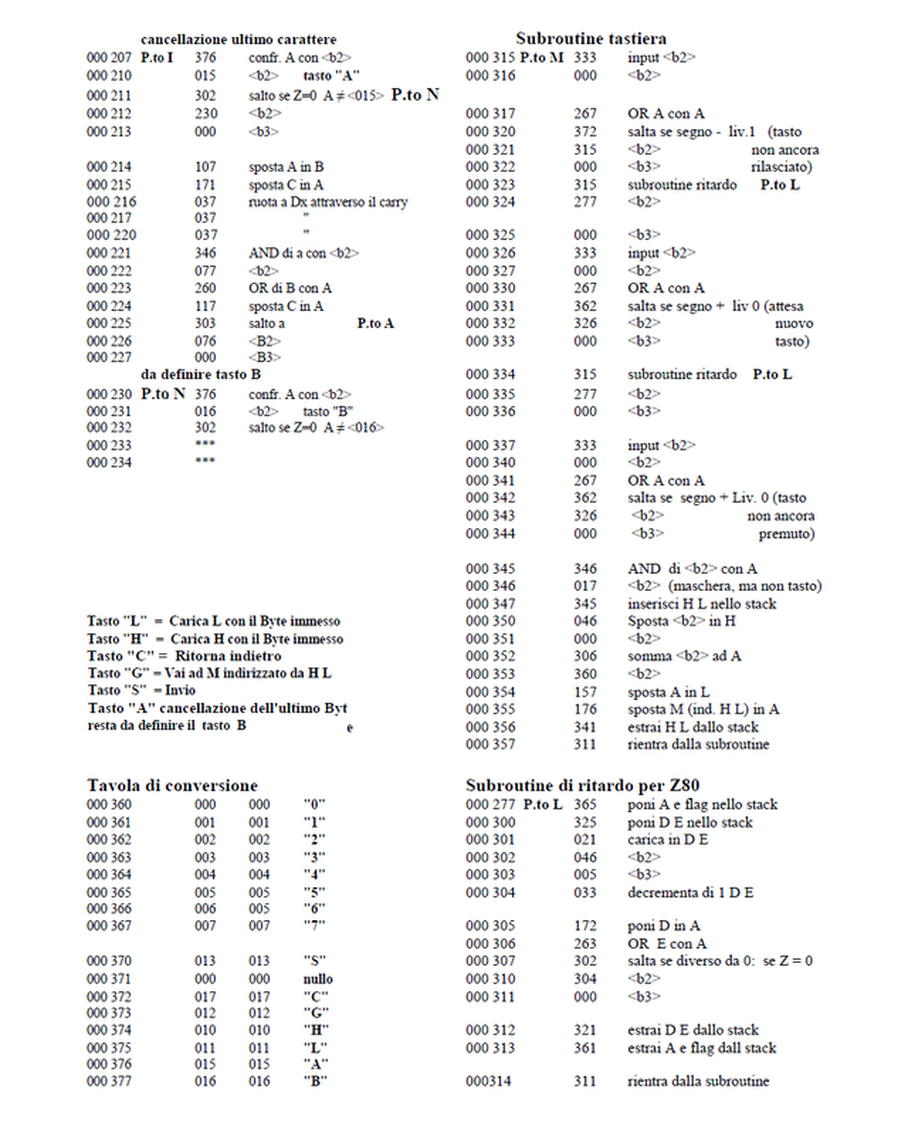

Schema n.3 e4: trattano la configurazione circuitale completa della memoria: 8 x 2 KB + 2 x 8 KB + 1 x 32 KB che comprende anche il bus indirizzi, il bus dati, il bus di stato (MEM/RQ, WR, RD) relativi.

La successione degli eventi è nella seguente sequenza:l

l'emissione degli indirizzi che avviene sul bus A0-A15;

segue la richiesta di memoria con l'attivazione (livello L) di una linea chiamata "MEMORY REQUEST", ossia richiesta di memoria (MEM/RQ);

infine avviene la lettura dalla memori o la scrittura in memoria con il bus dati D0-D7.

Facendo un passo indietro:

non è necessario introdurre nel sistema la totalità della memoria, è stato per fornirvi varie possibilità di scelta che ho adottato un sistema così variato in capacità; sceglierete voi la configurazione più adatta alle vostre esigenze, sfrondando il troppo ed il vano.

Io, in prima battuta, ero partito (anni '80) con una 2716 + due HM6116, che, allora, come adesso, costavano un patrimonio.

Ma allora valeva il principio dei banchi a bassa capacità, perché, nel caso di guasti (basta una sola cella difettosa), si rimpiazzava il cip in avaria spostando di un posto quelli funzionanti, poi con comodo eventualmente si sostituiva.

Se invece si fosse guastato un unico cip da 8 o 16 o 32 KB (costi stratosferici), sarebbero stati dolori veri e propri di parto.

Oggi, per contro, costano un'inezia i banchi da 8, 16, 32 KB (1 o 2 Euro) e sono assai cari quelli da 2 KB (6-8 Euro).

Alcuni anni fa c'è stato il momento in cui lo Z80 aveva un prezzo "irrisorio" (2-3 Euro), adesso il costo dei pochi esemplari rimasti è molto più alto.

Dicevo non è necessario, per il vostro divertimento, introdurre tanta memoria RAM: è sufficiente un cip Eprom (2 KB) e al più 4 KB di RAM. Allo scopo utilizzerete solo la parte di decodifica (SN74138 evidenziato con un riquadro nello schema n.1) che vi serve, l'altra parte resterà disponibile per eventuali aggiunte. Se vi necessitasse più Eprom (un altro cip da 2 KB) lo potrete porre in sostituzione di un cip RAM con la sola modifica sui pin 20 e 21: scollegate il pin 20 dal pin 18 e su di esso collegherete WR/RD; sul pin 21 che resta libero porrete un diodo con l'anodo verso l'alimentazione.

Il modello base (necessario e sufficiente) consterebbe, pertanto, della scheda madre con 2 KB RAM e 2KB Eprom + tastierino + visualizzatore ottale + relative decodifiche, tutto qui.

La scelta circa la comunicazione con le periferiche è stato misto: non in mappa di memoria pura, ma con appoggio, per il trasferimento dati, su sistema di ingresso/uscita ( I/O), pertanto passiamo agli schemi 5 e 6.

La successione degli eventi è nella seguente sequenza:l

l'emissione degli indirizzi che avviene sul bus A0-A15;

segue la richiesta di memoria con l'attivazione (livello L) di una linea chiamata "MEMORY REQUEST", ossia richiesta di memoria (MEM/RQ);

infine avviene la lettura dalla memori o la scrittura in memoria con il bus dati D0-D7.

Facendo un passo indietro:

non è necessario introdurre nel sistema la totalità della memoria, è stato per fornirvi varie possibilità di scelta che ho adottato un sistema così variato in capacità; sceglierete voi la configurazione più adatta alle vostre esigenze, sfrondando il troppo ed il vano.

Io, in prima battuta, ero partito (anni '80) con una 2716 + due HM6116, che, allora, come adesso, costavano un patrimonio.

Ma allora valeva il principio dei banchi a bassa capacità, perché, nel caso di guasti (basta una sola cella difettosa), si rimpiazzava il cip in avaria spostando di un posto quelli funzionanti, poi con comodo eventualmente si sostituiva.

Se invece si fosse guastato un unico cip da 8 o 16 o 32 KB (costi stratosferici), sarebbero stati dolori veri e propri di parto.

Oggi, per contro, costano un'inezia i banchi da 8, 16, 32 KB (1 o 2 Euro) e sono assai cari quelli da 2 KB (6-8 Euro).

Alcuni anni fa c'è stato il momento in cui lo Z80 aveva un prezzo "irrisorio" (2-3 Euro), adesso il costo dei pochi esemplari rimasti è molto più alto.

Dicevo non è necessario, per il vostro divertimento, introdurre tanta memoria RAM: è sufficiente un cip Eprom (2 KB) e al più 4 KB di RAM. Allo scopo utilizzerete solo la parte di decodifica (SN74138 evidenziato con un riquadro nello schema n.1) che vi serve, l'altra parte resterà disponibile per eventuali aggiunte. Se vi necessitasse più Eprom (un altro cip da 2 KB) lo potrete porre in sostituzione di un cip RAM con la sola modifica sui pin 20 e 21: scollegate il pin 20 dal pin 18 e su di esso collegherete WR/RD; sul pin 21 che resta libero porrete un diodo con l'anodo verso l'alimentazione.

Il modello base (necessario e sufficiente) consterebbe, pertanto, della scheda madre con 2 KB RAM e 2KB Eprom + tastierino + visualizzatore ottale + relative decodifiche, tutto qui.

La scelta circa la comunicazione con le periferiche è stato misto: non in mappa di memoria pura, ma con appoggio, per il trasferimento dati, su sistema di ingresso/uscita ( I/O), pertanto passiamo agli schemi 5 e 6.

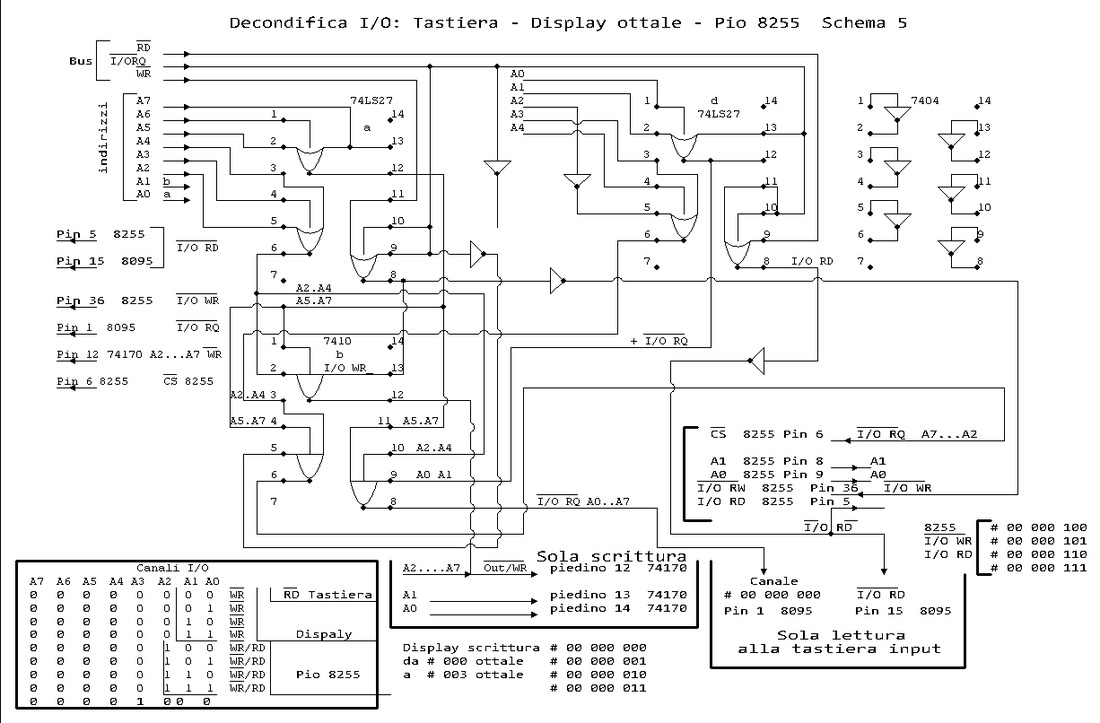

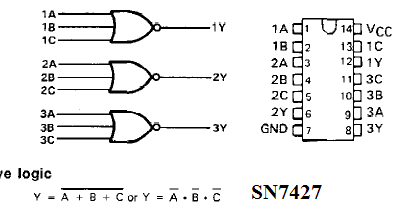

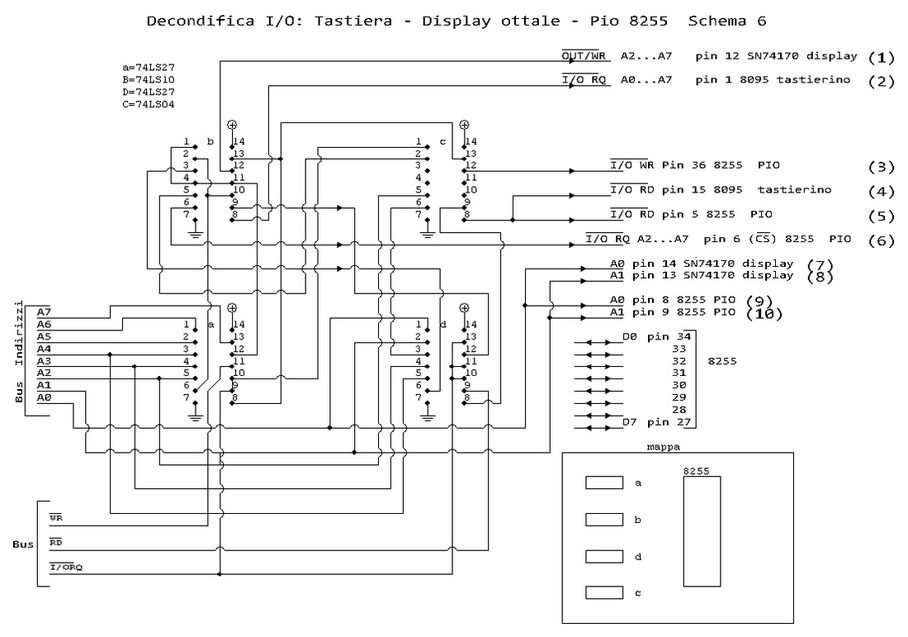

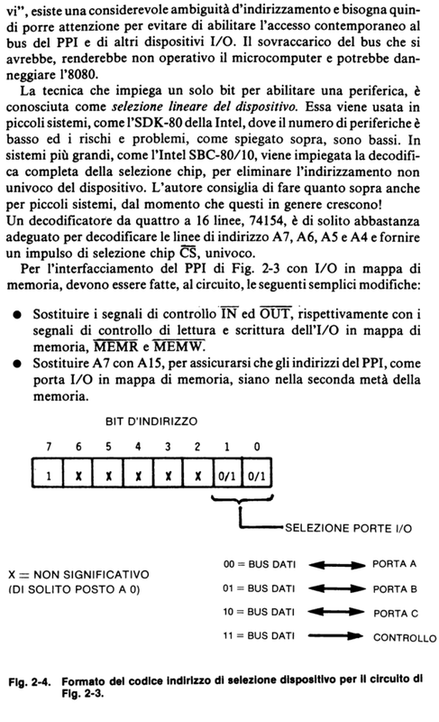

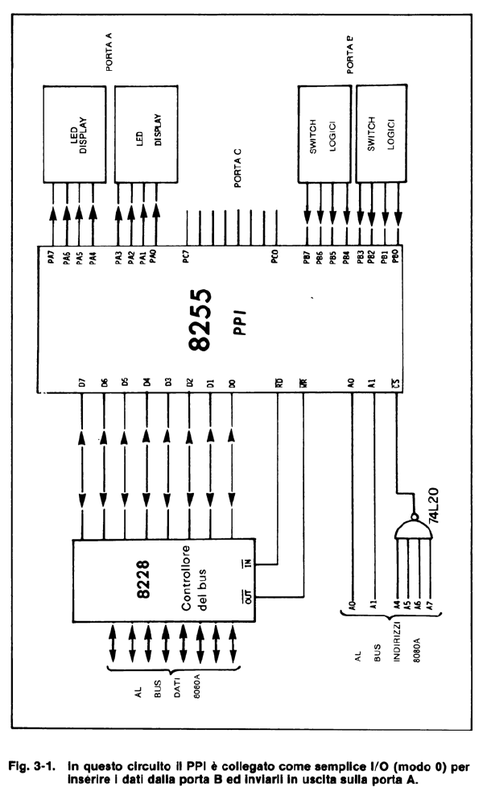

Schema n. 5 (schema 6): è un circuito di decodifica assoluto di indirizzi e segnali di comando che consente operazioni di ingresso/uscita sulle porte di comunicazione:

la porta # 000 ottale di ingresso (read) dal tastierino (istruzione 333);

le porte # 000, 001, 002, 003 di uscita (write) per il visualizzazione (istruzione 323);

le porte # 004, 005, 006, 007 di ingresso uscita (read/write) che servono, volendo montare anche la PIO 8255;

Nel disegno viene raffigurata la mappa delle porte (sulla sinistra) e, su ogni terminazione, sono specificatamente indicati i collegamenti ai successivi circuiti: tastierino, display, PIO 8255.

Lascerete inutilizzato quanto non riterrete di adoperare (ad esempio l'8255).

Come sapete il sistema I/O prevede l'emissione degli indirizzi sui primi otto bit del bus indirizzi A0-A7 (replicato sui secondi 8 bit), la richiesta avviene con l'attivazione (livello L) della linea "INPUT/OUTPUT REQUEST": I/O RQ, segue, in ultimo, la lettura o scrittura dati.

Trattandosi di un bus parallelo di 8 bit (A0-A7) il numero massimo di dispositivi indirizzabile è di 256, ossia

2^1 + 2^2 +2^3 + 2^4 + 2^5 + 2^6 + 2^7 + 2^8 = 256.

La traduzione da binario in decimale avviene, come in tutti i sistemi posizionali non ridondanti, usando le potenze crescenti della base, nel caso specifico di due; quindi chiamando a, b,c,d,e,f,g,h le cifre posizionali del numero, avremo:

numero binario = a x 2^0 + b x 2^1 + c x 2^2 + d x 2^3 + e x 2^4 + f x 2^5 + g x 2^6 + h x 2^7 = numero decimale.

In realtà in binario il numero sarà 255 + la locazione zero e sarà così concepito 11 111 111 (infatti considerando il primo numero, cioè lo zero, conteremo fino ad un massimi di 255, così come in decimale con tre cifre conteremo fino a 999, ma con lo zero saranno 1000 numeri). Ho diviso le otto cifre in gruppi, secondo il sistema di lettura ottale (non chiedetemi il sistema esadecimale, perché mi ci vorrebbe troppo tempo poi per decodificare, a memoria, i numeri. Nel caso sopra sarebbe 111 111, ossia FF).

Se a ciascun gruppo assegnamo il corrispondente numero decimale avremo 377, poiché 11 = 3 e 111 = 7.

Allora si tratta solo di memorizzare le cifre da 0 a 7

000 = 0 100 = 4 Esempio: 10 100 011 = 243 ottale

001 = 1 101 = 5 Esempio: 11 010 101 = 325 ottale

010 = 2 110 = 6 Esempio 00 111 110 = 076 ottale

011 = 3 111 = 7 Esempio 11 111 111 = 377 ottale

A questo punto divideremo anche il bus indirizzi a 16 bit in due semibus da otto: la parte più significativa, che chiameremo H xx xxx xxx, da A8 ad A15

e la parte meno significativa, che chiameremo L xx xxx xxx, da A0 ad A7

I codici operativi stessi e le istruzione in codice macchina devono dividere in due il bus indirizzi,

infatti non potrebbero comunicarlo alla CPU in una sola istruzione, trattandosi di bus di comunicazione dati a otto bit.

Avremo, per lo Z80, istruzioni a uno, due e tre Byte, di cui il primo è sempre un codice operativo.

Troverete ampi dettagli sulle pubblicazioni: "Esperimenti con TTL e 8080" volo 1° e 2°.

http://isoondaomradio.weebly.com/8080-e-z80-i-nanocomputers.html

Lo schema n. 6 è la traduzione da schema di principio in schema pratico dello schema 5.

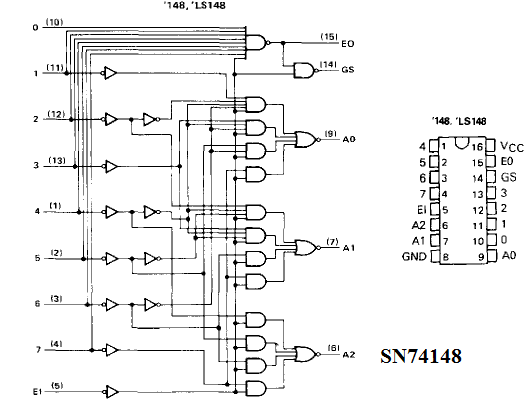

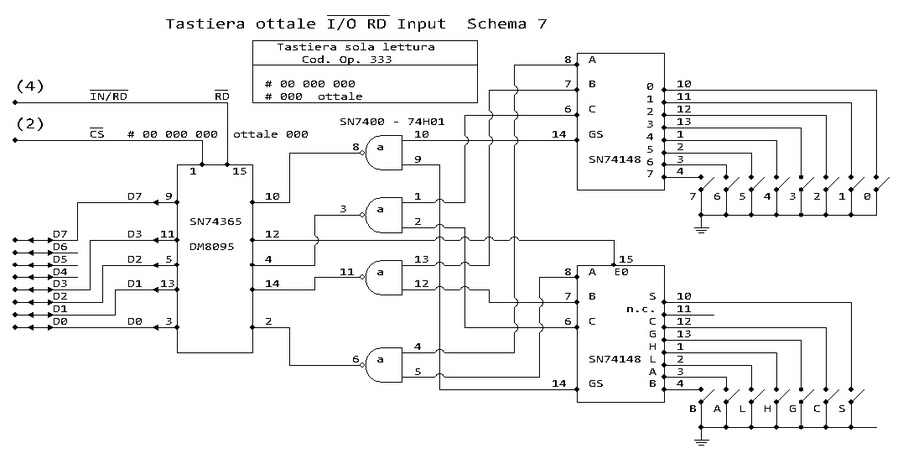

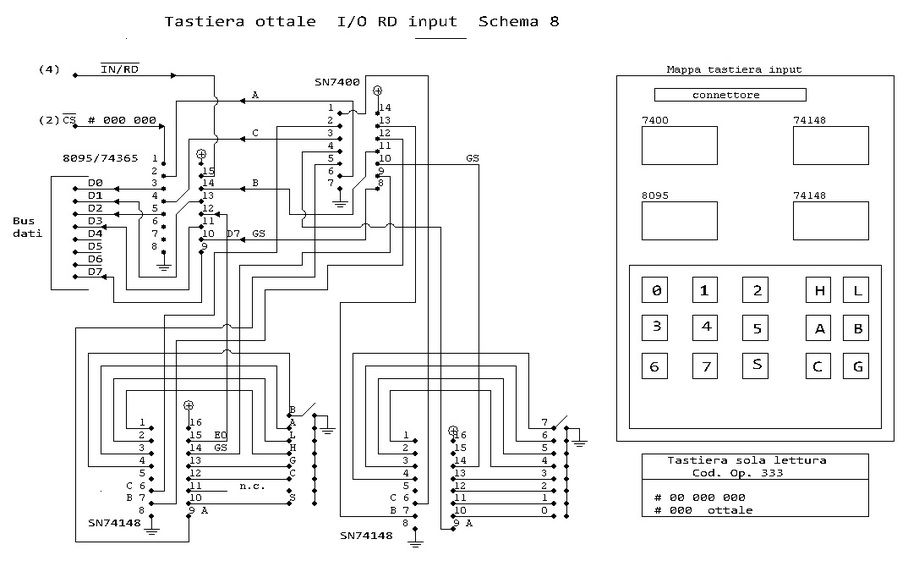

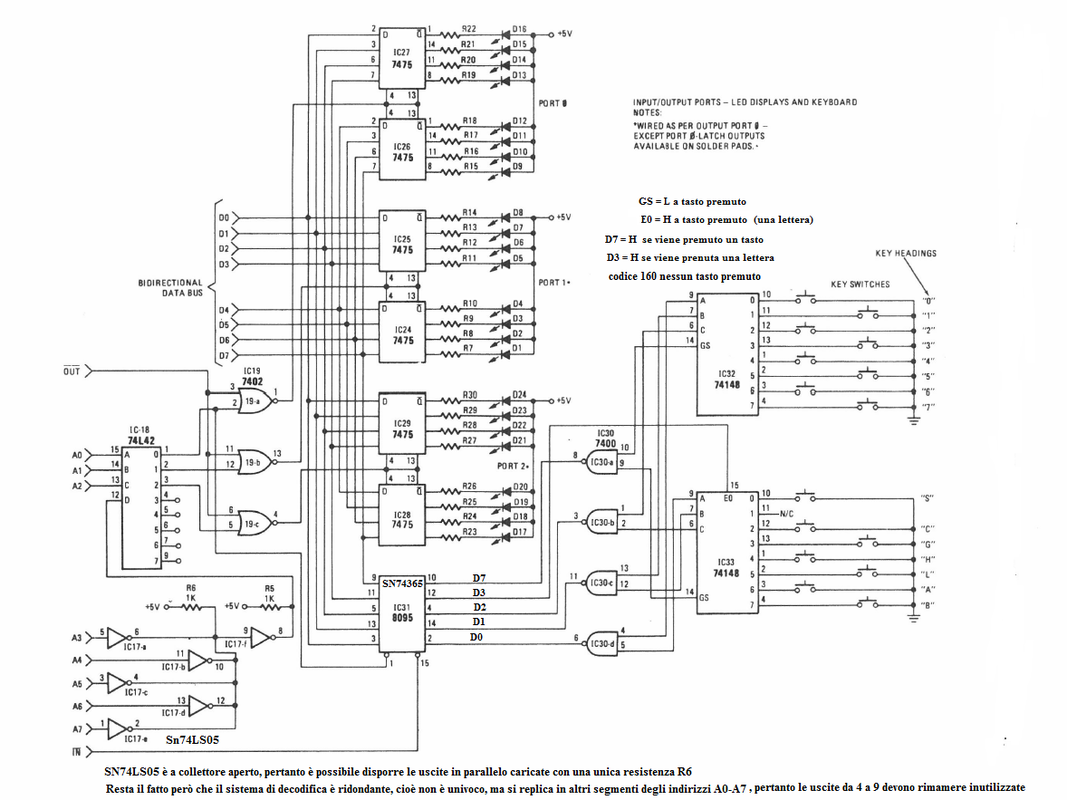

Nello schema n. 7 è configurato il circuito del tastierino, comprendente 15 tast di cui:

i numeri dallo 0 al 7;

le lettere A, B, C, G, H, L, S (si intende che tali tasti potrete denominarli anche come più vi garba).

I dati vengono trasferiti sui primi tre bit da D0 a D2 e in appoggio sul bit D3 e D7.

Il bit D7, quando è attivo H, indica che è stato premuto un tasto qualsiasi: il bit D3, quando è attivo H, indica che è stata premuta una lettera. Il codice generato quando non è premuto nessun tasto è 160 ottale.

Gli otto numeri sono quelli del linguaggio ottale (che verranno immessi in memoria e visualizzati, nan mano, uno alla volta) le sette lettere riguardano i comandi ad uso dell'operatore e, naturalmente, non verranno visualizzati, se ne vedrà solo l'effetto.

Il tasto "S" corrisponde al nostro invio (Enter): immette in memoria il numero ottale (byte) che deve essere digitato come un complesso di tre numeri e fa incrementare di uno la coppia di registri H ed L della CPU, che puntano la locazione corrente di memoria.

Esempio: il byte 11 111 110 = 376 ottale, andrà immesso una cifra alla volta: il tre, seguito dal sette e dal sei, poi verrà premuto "S", che memorizzerà nella locazione corrente e farà avanzare H L verso la locazione successiva per la prossima immissione.

Il tasto H comanda alla CPU di immettere il contenuto del byte digitato, nella parte più significativa H del registro a 16 bit degli indirizzi.

Il tasto L comanda alla CPU di immettere il contenuto del byte digitato nella parte meno significativa L del registro a 16 bit degli indirizzi. Tanto i contenuti di H quanto quelli di L saranno visualizzati sul display, di cui parlerò tra poso.

Con tali tasti (H ed L) potrete scegliere l'indirizzo di inizio (in qualunque parte della memoria RAM) di quanto vorrete introdurre circa i programmi che scriverete o vorrete provare.

Il tasto "G" (go, vai) lancia il programma a partire dalla locazione corrente (quella visualizzata sul display), pertanto una volta immesso il listato di un programma, dovrete, con i tasti H ed L, tornare alla locazione di inizio e premere "G", per vederne l'esecuzione.

Se invece reimmetterete con H ed L l'indirizzo di partenza del programma e poi pigerete, a più riprese, "S" potrete rivedere, byte per byte, quanto avete scritto.

I l tasto "C" produce il decremento di 1 dei registri H ed L (in particolare di L) ed il ritorno indietro di una locazione di memoria.

I tasti "A" e "B" sono vuoti e disponibili a diventare comandi a seguito di programmazione dedicata.

i numeri dallo 0 al 7;

le lettere A, B, C, G, H, L, S (si intende che tali tasti potrete denominarli anche come più vi garba).

I dati vengono trasferiti sui primi tre bit da D0 a D2 e in appoggio sul bit D3 e D7.

Il bit D7, quando è attivo H, indica che è stato premuto un tasto qualsiasi: il bit D3, quando è attivo H, indica che è stata premuta una lettera. Il codice generato quando non è premuto nessun tasto è 160 ottale.

Gli otto numeri sono quelli del linguaggio ottale (che verranno immessi in memoria e visualizzati, nan mano, uno alla volta) le sette lettere riguardano i comandi ad uso dell'operatore e, naturalmente, non verranno visualizzati, se ne vedrà solo l'effetto.

Il tasto "S" corrisponde al nostro invio (Enter): immette in memoria il numero ottale (byte) che deve essere digitato come un complesso di tre numeri e fa incrementare di uno la coppia di registri H ed L della CPU, che puntano la locazione corrente di memoria.

Esempio: il byte 11 111 110 = 376 ottale, andrà immesso una cifra alla volta: il tre, seguito dal sette e dal sei, poi verrà premuto "S", che memorizzerà nella locazione corrente e farà avanzare H L verso la locazione successiva per la prossima immissione.

Il tasto H comanda alla CPU di immettere il contenuto del byte digitato, nella parte più significativa H del registro a 16 bit degli indirizzi.

Il tasto L comanda alla CPU di immettere il contenuto del byte digitato nella parte meno significativa L del registro a 16 bit degli indirizzi. Tanto i contenuti di H quanto quelli di L saranno visualizzati sul display, di cui parlerò tra poso.

Con tali tasti (H ed L) potrete scegliere l'indirizzo di inizio (in qualunque parte della memoria RAM) di quanto vorrete introdurre circa i programmi che scriverete o vorrete provare.

Il tasto "G" (go, vai) lancia il programma a partire dalla locazione corrente (quella visualizzata sul display), pertanto una volta immesso il listato di un programma, dovrete, con i tasti H ed L, tornare alla locazione di inizio e premere "G", per vederne l'esecuzione.

Se invece reimmetterete con H ed L l'indirizzo di partenza del programma e poi pigerete, a più riprese, "S" potrete rivedere, byte per byte, quanto avete scritto.

I l tasto "C" produce il decremento di 1 dei registri H ed L (in particolare di L) ed il ritorno indietro di una locazione di memoria.

I tasti "A" e "B" sono vuoti e disponibili a diventare comandi a seguito di programmazione dedicata.

Lo schema n.8 è la traduzione da schema elettrico in schema pratico dello schema n. 7.

Il tastierino naturalmente ha bisogno di un programma residente in Eprom per funzionare; di questo vi darò a suo tempo il listato da trasferire su memoria Eprom.

E qui cominciano i guai: per trasferire il programma (diciamo il Bios, per intenderci) su Eprom dovrete servirvi di un programmatore di Eprom (ve ne darò lo schema, tutta farina del mio sacco, come tutto il resto).

Inoltre dovrete avere a disposizione una lampada a raggi ultravioletti (vi parlerò anche di quella) per la cancellazione eventuale del contenuto della Eprom, qualora fosse di recupero o di seconda mano o se commetterete qualche errore, mentre la scrivete (per ora diciamo pure che non sono possibili sovrascritture su di una stessa cella).

Il tastierino naturalmente ha bisogno di un programma residente in Eprom per funzionare; di questo vi darò a suo tempo il listato da trasferire su memoria Eprom.

E qui cominciano i guai: per trasferire il programma (diciamo il Bios, per intenderci) su Eprom dovrete servirvi di un programmatore di Eprom (ve ne darò lo schema, tutta farina del mio sacco, come tutto il resto).

Inoltre dovrete avere a disposizione una lampada a raggi ultravioletti (vi parlerò anche di quella) per la cancellazione eventuale del contenuto della Eprom, qualora fosse di recupero o di seconda mano o se commetterete qualche errore, mentre la scrivete (per ora diciamo pure che non sono possibili sovrascritture su di una stessa cella).

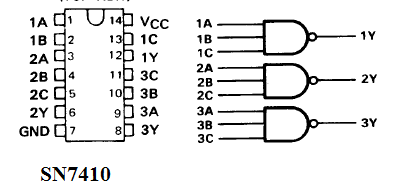

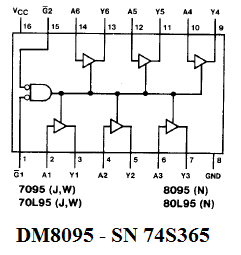

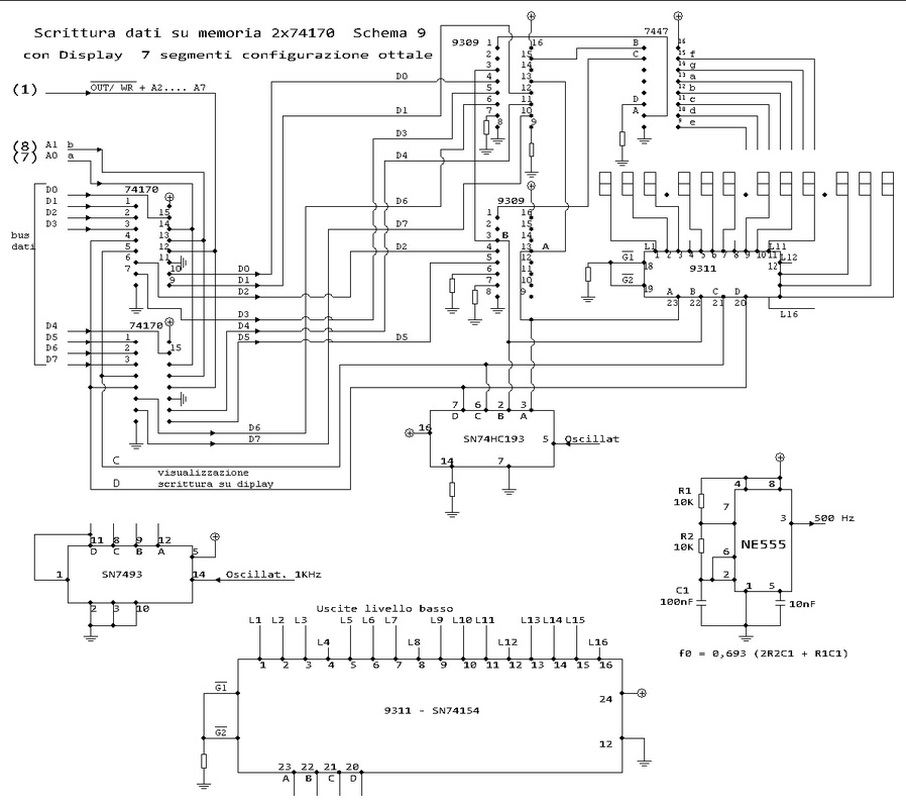

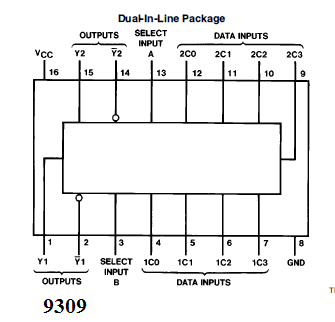

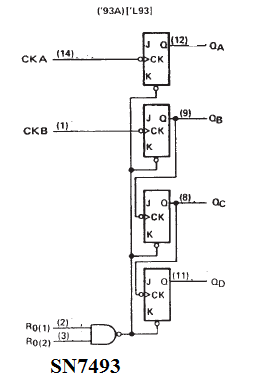

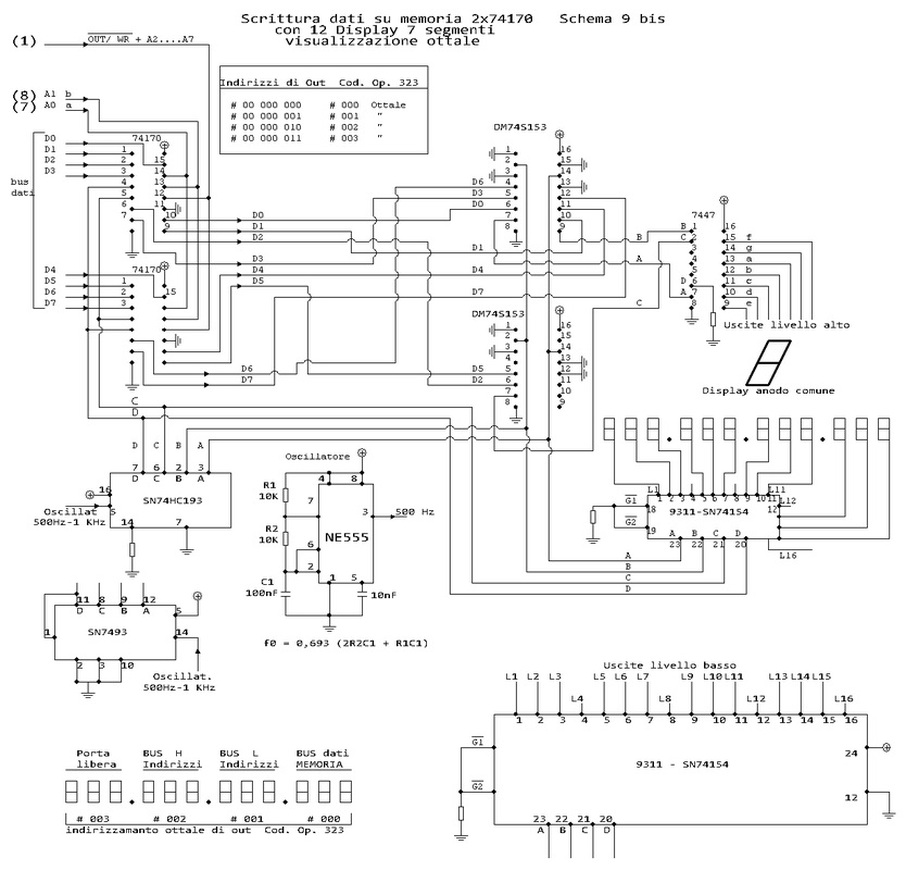

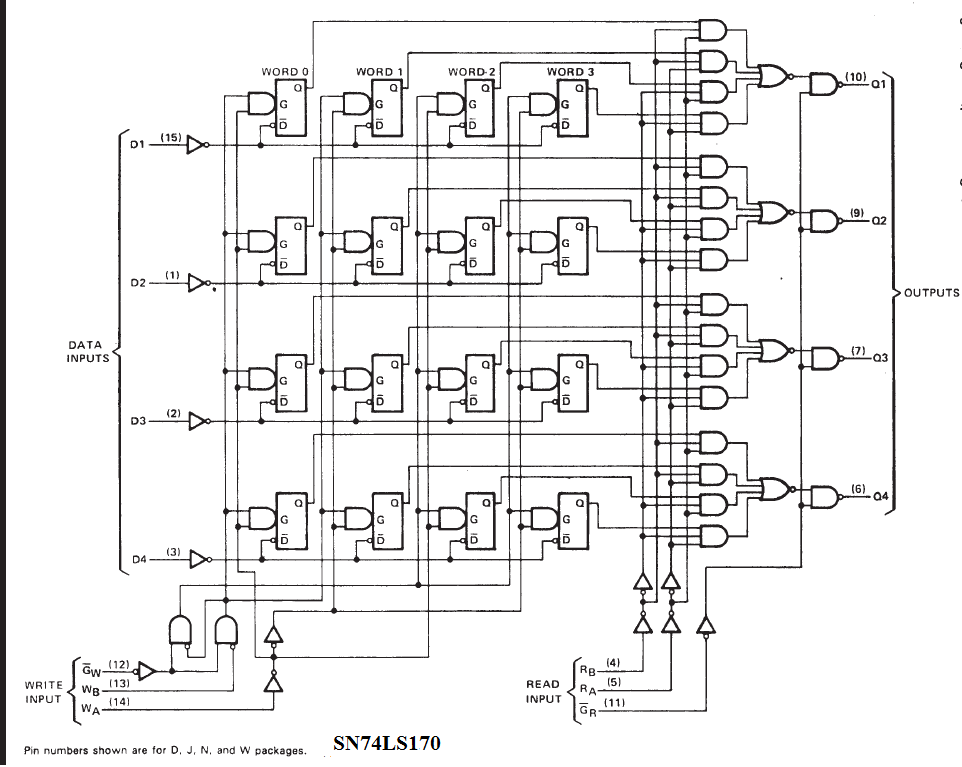

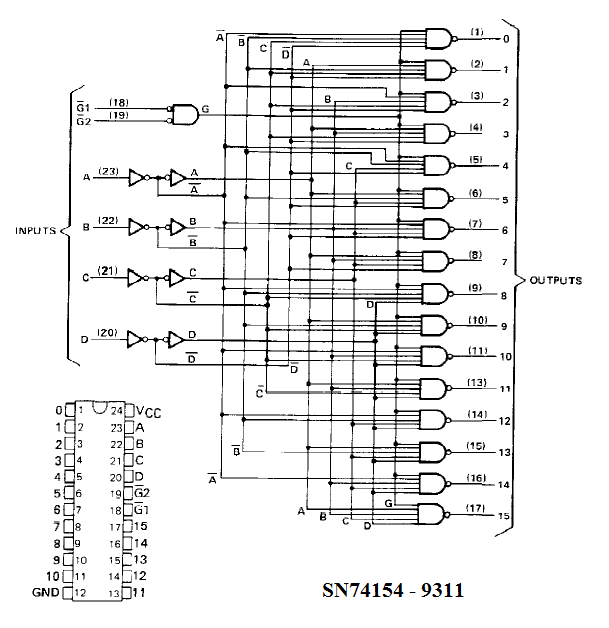

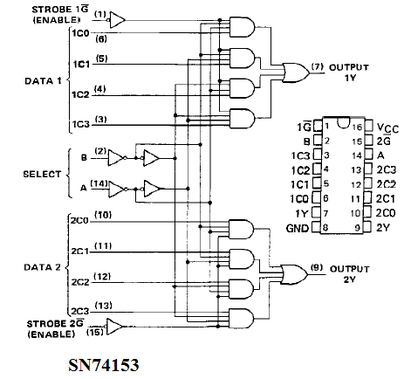

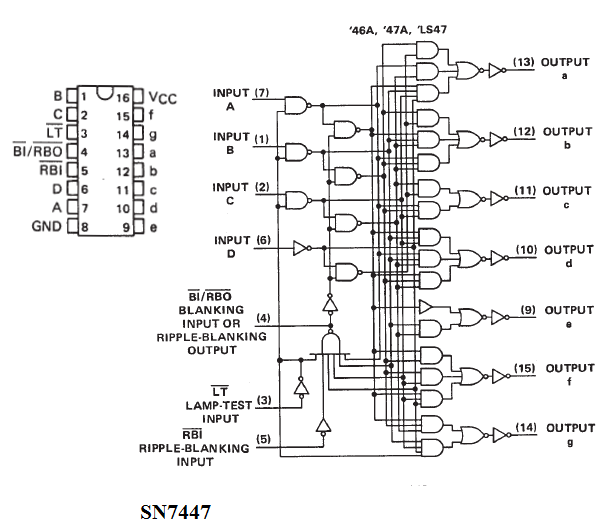

L'integrato SN74170 consta di 4 banchi di memoria RD/WR di quattro bit. Gli indirizzi binari di scrittura sono dati da WA e WB, mentra quelli binari di lettura sono dati da RA ed RB. Con due SN74170 in parallelo si ottiengono 4 Byte completi. Pertanto possiamo memorizzare permanentemente il contenuto di quattro porte di I/O (ndirizzi 000, 001, 002, 003 ottali) e trasferirne il contenuto sul lettore a display multiplexato. Ciò avviene selezionando in successione i contenuti degli SN74170, trasferendoli opportunamente sull'SN74153 e sull'SN7447 che li traducono in forma ottale e infine visualizzandoli in rapidissima successione per mezzo del 9311. La sequenza di lettura è pilotata dall'SN7493 (SN74HC193).

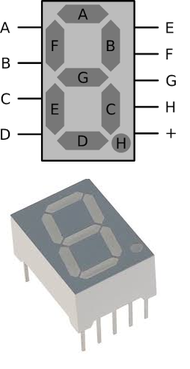

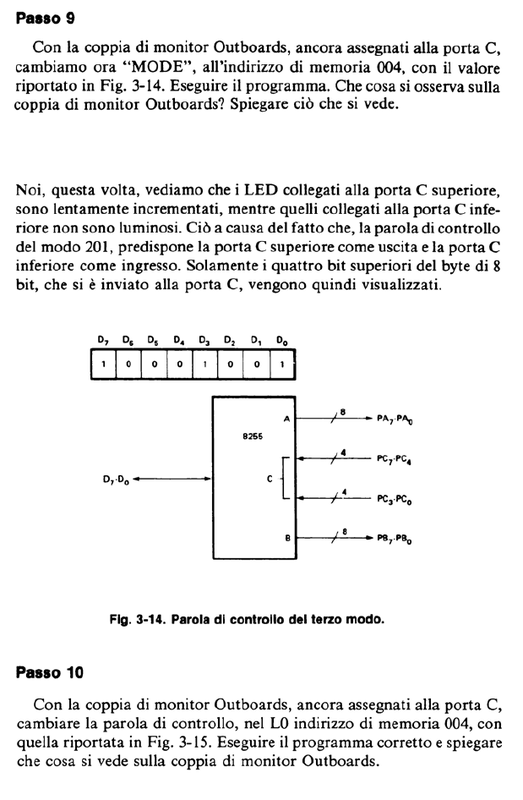

Lo schema n.9-9 bis riguarda il visualizzatore, composto da 12 display a sette segmenti, disposti in batterie da tre (per visualizzare in ottale).

Per l'occasione io ho adoperato, reperito ad una fiera, il display a 16 cifre di una calcolatrice scientifica tascabile, lasciandone quattro spente in modo da separare gli altri dodici in gruppi di tre.

Il gruppo più a destra è dedicato al contenuto numerico della locazione di memoria puntata correntemente; i successivi due gruppi indicano rispettivamente l'indirizzo basso L e quello alto H dei registri H ed L, correntemente puntati; il gruppo più a sinistra è un byte disponibile di uso generale, che può essere usato da un vostro programma con indirizzamento specifico.

I due schemi (9 e 9 bis) di visualizzazione sono identici di principio, differiscono solo per l'uso dell'SN74S153 al posto del 9309, inoltre, in essi, viene data una doppia configurazione con SN7493 e SN74HC193.

I dati che pervengono al Display sono indirizzati a quattro locazioni di memoria degli SN74170 con i seguenti indirizzi ottali: #000, #001, #002, #003 in modalità scrittura.

Due SN74170 in parallelo implementano un intero Byte: 4 bit + 4 bit .

Un circuito aggiuntivo (SN74 S153, SN7493, SN7447, SN 74154) provvede, senza interferire con la CPU, a leggere in sequenza i dati immagazzinati nelle quattro celle da un byte cadauna(Sn74170), trasferendoli (con sistema multiplexer) su quattro gruppi di visualizzatori a sette segmenti; il circuito stesso permette. decodificando oppropriatamente, la lettura in sistema ottale del contenuto di ogni singolo Byte.

Tutti i circuiti sono stati da me ideati e collaudati, onde il sistema completo funziona perfettamente.

Un sistema molto più semplice di immissione dati e di lettura viene illustrato nel successivo schema tratto dal Bugbook VI (Jackson) a pagina 20-27.

La lettura (in sistema ottale) avviene a seconda della configurazione con cui si illuminano i led.

Per l'occasione io ho adoperato, reperito ad una fiera, il display a 16 cifre di una calcolatrice scientifica tascabile, lasciandone quattro spente in modo da separare gli altri dodici in gruppi di tre.

Il gruppo più a destra è dedicato al contenuto numerico della locazione di memoria puntata correntemente; i successivi due gruppi indicano rispettivamente l'indirizzo basso L e quello alto H dei registri H ed L, correntemente puntati; il gruppo più a sinistra è un byte disponibile di uso generale, che può essere usato da un vostro programma con indirizzamento specifico.

I due schemi (9 e 9 bis) di visualizzazione sono identici di principio, differiscono solo per l'uso dell'SN74S153 al posto del 9309, inoltre, in essi, viene data una doppia configurazione con SN7493 e SN74HC193.

I dati che pervengono al Display sono indirizzati a quattro locazioni di memoria degli SN74170 con i seguenti indirizzi ottali: #000, #001, #002, #003 in modalità scrittura.

Due SN74170 in parallelo implementano un intero Byte: 4 bit + 4 bit .

Un circuito aggiuntivo (SN74 S153, SN7493, SN7447, SN 74154) provvede, senza interferire con la CPU, a leggere in sequenza i dati immagazzinati nelle quattro celle da un byte cadauna(Sn74170), trasferendoli (con sistema multiplexer) su quattro gruppi di visualizzatori a sette segmenti; il circuito stesso permette. decodificando oppropriatamente, la lettura in sistema ottale del contenuto di ogni singolo Byte.

Tutti i circuiti sono stati da me ideati e collaudati, onde il sistema completo funziona perfettamente.

Un sistema molto più semplice di immissione dati e di lettura viene illustrato nel successivo schema tratto dal Bugbook VI (Jackson) a pagina 20-27.

La lettura (in sistema ottale) avviene a seconda della configurazione con cui si illuminano i led.

Non dimenticata che l'alimentazione deve essere compresa tra 4,7 e 5,2-5,3 V, allo scopo prossimamente vi fornirò lo schema di un alimentatore stabilizzato adatto, aggiungerò successivamente:

lo schema per il programmatore di Eprom, il listato del "bios" di tastiera ottale;

lo schema riguardante la PIO 8255;

lo schema per un display alfanumerico a 16 cifre con quattro HPDL2416

lo schena di un attuatore in grado di controllare e pilotare apparecchiature di vario genere.

lo schema per il programmatore di Eprom, il listato del "bios" di tastiera ottale;

lo schema riguardante la PIO 8255;

lo schema per un display alfanumerico a 16 cifre con quattro HPDL2416

lo schena di un attuatore in grado di controllare e pilotare apparecchiature di vario genere.

|

Sulla sinistra c'è la mappa di tutta la memoria ram, secondo la suddivisione ipotizzata dal progetto.

E' indispensabile almeno un banco di memoria Eprom, sulla quale scrivere il sistema di "bios", con il quale far funzionare la tastiera ottale di cui allo schema n. 7 e 8. Seguono sette banchi di memoria ram da 2 KB, due banchi di ram da 8 KB e un banco da 32 KB. Come già detto non è tassativo implementare tanta memoria ram: il minimo è costituito da un banco di Eprom ed uno di Ram. Nel listato seguente, che riguarda il "bios" vedrete alcuni indirizzi preceduti da asterisco: tali indirizzi saranno modificati in funzione della quantità di memoria che voi implementerete. Dal canto mio ho identificato i suddetti indirizzi nell'ipotesi di 64 KB di memoria. Pertanto il puntatore dello Stack pointer (alle locazioni 000 071 e 000 072) è fissato a 377 377 cioè alla fine della memoria; mentre i registri H ed L (alle locazioni 000 074 e 000 075) sono puntati all'inizio della Ram, ossia a 010 000. Nulla vieta di sostituirli con altre posizioni, a vostra scelta |

Ci sono da definire le locazioni: # 000 010, 000 020, 000 030, 000 040, 000 050, 000 060 e 000 070, che io ho lasciato riempite solo con asterischi.

Tali locazioni sono puntate da alcune istruzioni dello Z80 come richiami di subroutine e sono le seguenti:

317 chiama la subroutine all'indirizzo 000 010

327 chiama la subroutine all'indirizzo 000 020

337 chiama la subroutine all'indirizzo 000 030

347 chiama la subroutine all'indirizzo 000 040

357 chiama la subroutine all'indirizzo 000 050

367 chiama la subroutine all'indirizzo 000 060

377 chiama la subroutine all'indirizzo 000 070.

Non ritengo sia necessario definirle a priori, ma solo quando e se riterrete di servirvi di tali istruzioni, pertanto le lascerete vuote e le riempirete qualora se ne presentasse l'occasione.

Troverete il listato completo delle istruzioni dell'8080, valide anche per lo Z80, al seguente indirizzo

http://isoondaomradio.weebly.com/8080-e-z80-i-nanocomputers.html

Lo Z80, in realtà possiede un ulteriore numero di istruzioni, poiché porta in sé duplicati tutti i registri di uso generale: A, SP, B, C, D, E, H, L e possiede ancora altre istruzioni che andranno viste dettagliatamente più in là.

Le istruzioni che troverete dalla locazione 000 207 in poi "cancellazione dell'ultimo carattere", sono ipotesi recentissima dell'ultima ora, ma non sono state ancora provate, pertanto non prendetele per oro colato; avrei potuto concellarle e non presentarle nemmeno, ma oramai le avevo scritte per me e non avevo voglia di rifare il foglio. Al momento non consideratele, perchè il programma alla locazione

000 207 va modificato con un'istruzione di ritorno all'inizio di modo che anche se accidentalmente pigerete o A o B non succederà nulla.

La modifica:

000 207 303

000 210 076

000 211 000

Qualora trovasta qualcosa da attribuire ai tasti A e B, prenderete la Eprom, la riporterete sul programmatore e sovrascriverete così

000 207 074

000 210 301

000 211 377

così facendo porterete le tre locazioni tutte a 000, in modo che la CPU, scorrendole, interpreti: nessuna operazione. Poi continuerete con il vostro programma dalla locazione 000 212.

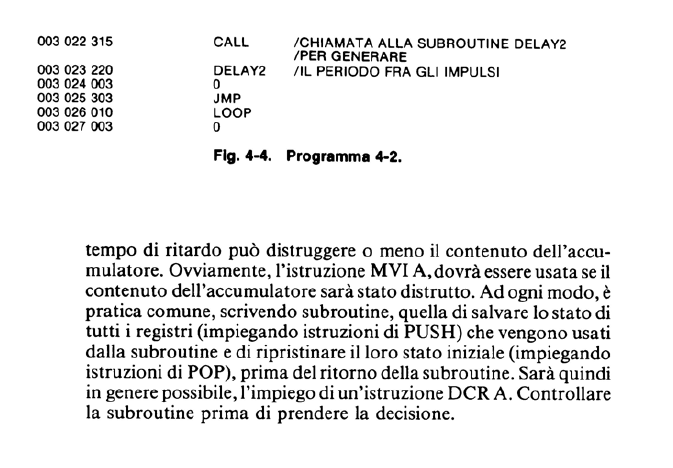

La parte più interessante è, senza dubbio, la subroutine di tastiera, con la quale(anche grazie alla sotto subroutine di ritardo # 000 277) si evita l'effetto rimbalzo dei contatti del tasto, quando viene premuto (indirizzo #000 315 e seguenti).

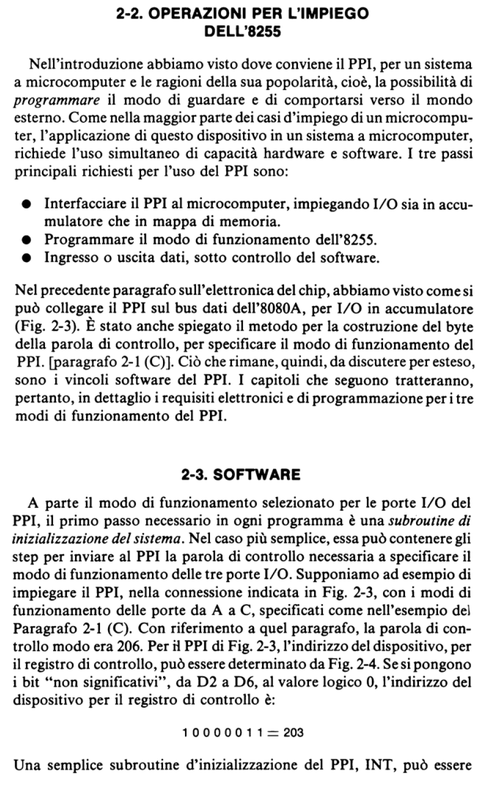

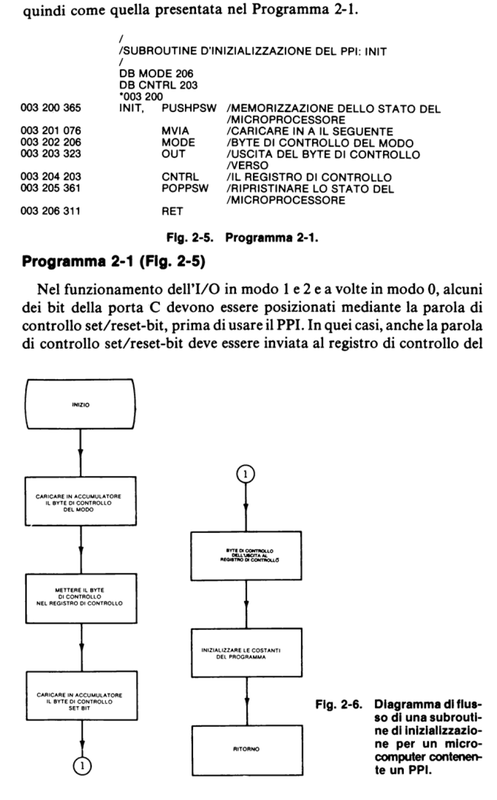

Ed ora il listato del "bios" di tastiera ottale:

E' giunto il momento di parlare del programmatore di Eprom e a questo punto è indispensabile una premessa:

purtroppo il programmatore è indispensabile, a meno che non troviate qualcuno che vi programmi la Eprom, cosa, del resto, non impossibile; con qualche decina di euro probabilmente vi ci mette anche la Eprom 2716, o, quantomeno, un'altra compatibile ed anche più veloce.

Mi raccomando non trascurate le modifiche, di cui sopra, al listato.

Tempo fa, anzi, mi era capitato sott'occhio, su Internet, l'indirizzo di un tizio che, appunto, si offriva di programmare qualsiasi tipo di tali cip.

Allora vi togliereste dallo stomaco un bel mattone, una bella spesa e potreste saltare, a piè pari, quanto riguarda il programmatore, che riprenderò in seguito , ma abbinadolo, molto più semplicemente, al nanocomputer, in qualità di periferica.

Il programmatore di Eprom

E' evidente che la Eprom deve essere nuova o vuota, se non lo fosse è necessario procedere alla sua cancellazione.

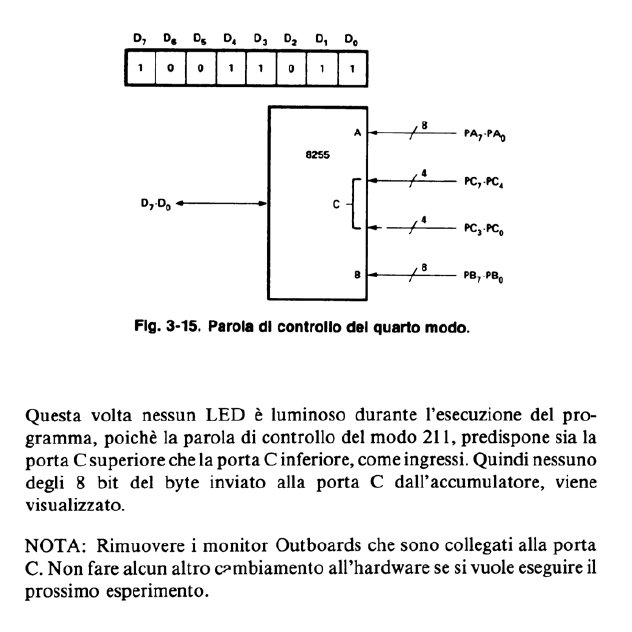

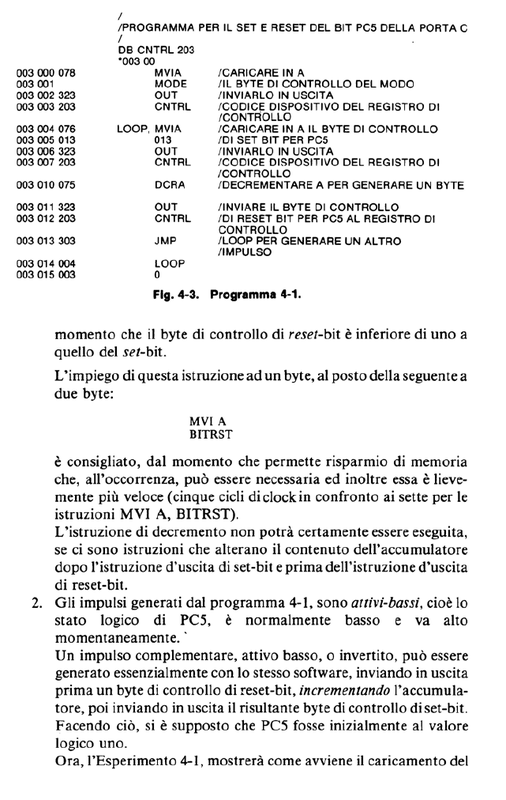

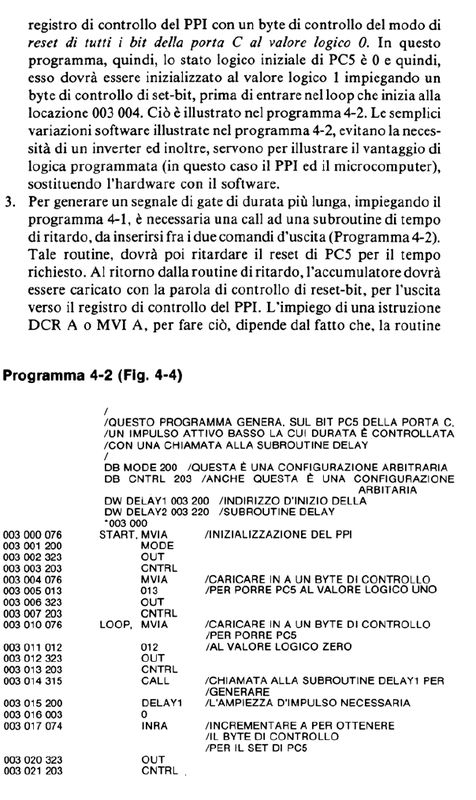

Ciò avviene esponendo la finestrella trasparente alla luce di una lampada UV del tipo presentato in figura 2, essa è la migliore in assoluto perché emette una luce non mi ricordo a quanti Armstrong di lunghezza d'onda, ma è ugualmente adatta quella di figura 3, più moderna.

Nel giro di una mezz'ora (max. un'ora) i contenuti della Eprom vengono completamente cancellati e la medesima è pronta per una nuova programmazione

purtroppo il programmatore è indispensabile, a meno che non troviate qualcuno che vi programmi la Eprom, cosa, del resto, non impossibile; con qualche decina di euro probabilmente vi ci mette anche la Eprom 2716, o, quantomeno, un'altra compatibile ed anche più veloce.

Mi raccomando non trascurate le modifiche, di cui sopra, al listato.

Tempo fa, anzi, mi era capitato sott'occhio, su Internet, l'indirizzo di un tizio che, appunto, si offriva di programmare qualsiasi tipo di tali cip.

Allora vi togliereste dallo stomaco un bel mattone, una bella spesa e potreste saltare, a piè pari, quanto riguarda il programmatore, che riprenderò in seguito , ma abbinadolo, molto più semplicemente, al nanocomputer, in qualità di periferica.

Il programmatore di Eprom

E' evidente che la Eprom deve essere nuova o vuota, se non lo fosse è necessario procedere alla sua cancellazione.

Ciò avviene esponendo la finestrella trasparente alla luce di una lampada UV del tipo presentato in figura 2, essa è la migliore in assoluto perché emette una luce non mi ricordo a quanti Armstrong di lunghezza d'onda, ma è ugualmente adatta quella di figura 3, più moderna.

Nel giro di una mezz'ora (max. un'ora) i contenuti della Eprom vengono completamente cancellati e la medesima è pronta per una nuova programmazione

Ma qualsiasi fonte di raggi UV, comprese le comuni lampade al neon o il sole, può effettuare la cancellazione in un certo numero di ore, pertanto dopo la programmazione è opportuno, per non aver sorprese, apporre un bollino opaco sulla finestrella trasparente della Eprom.

E' tuttavia possibile usare anche delle ROM (read only memory) non più cancellabili, ma è un azzardo perchè basta una svista, un errore e siete fregati.

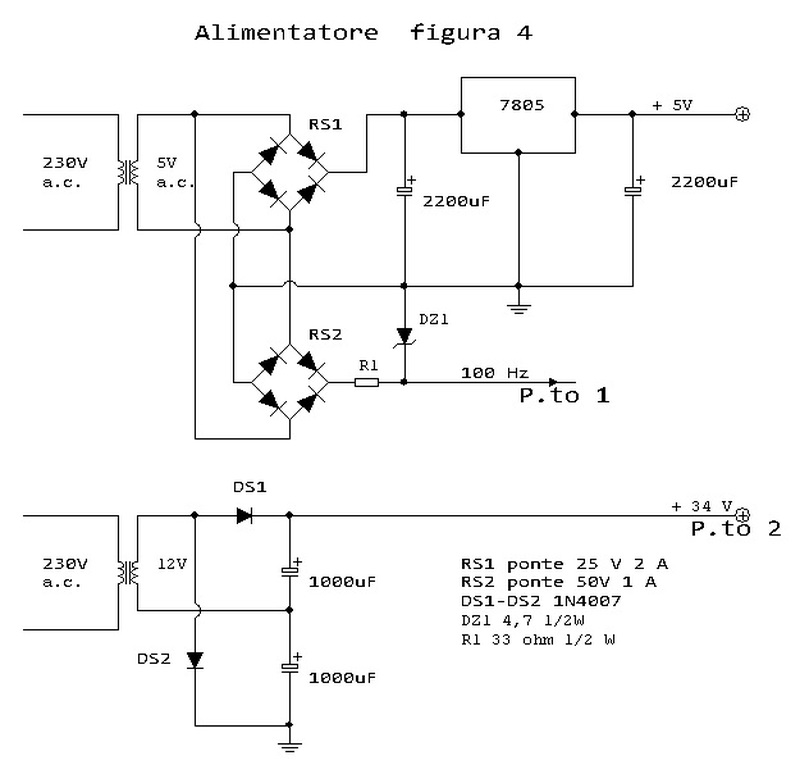

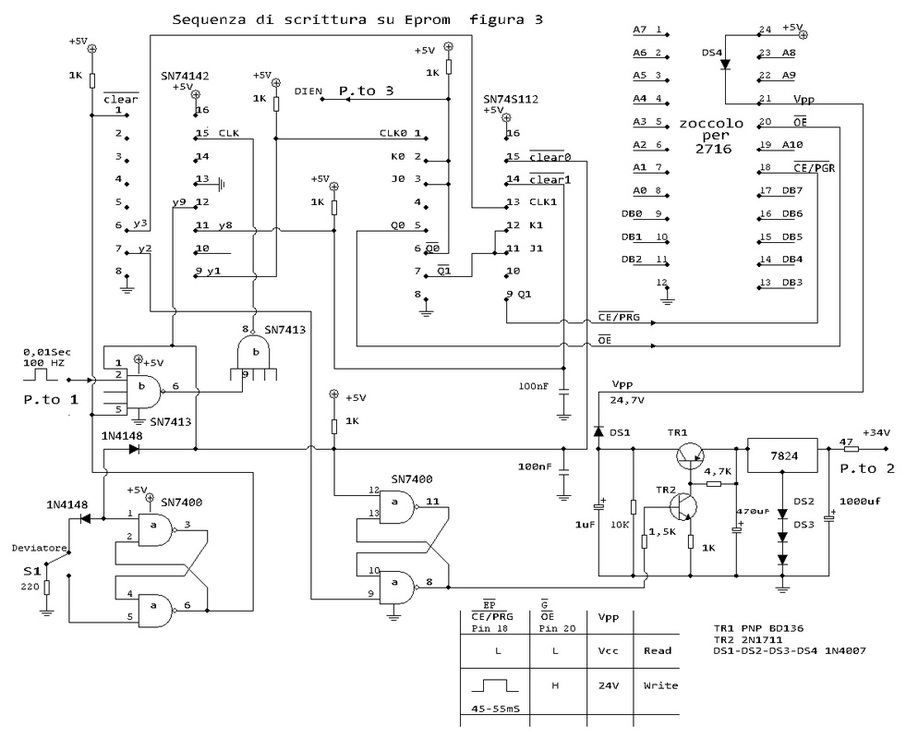

Partiamo dalla figura 4. Sono necessarie due alimentazioni stabilizzate: una a 5 volt per gli integrati e una a 34 volt (che sarà ridotta a circa 25 volt) per scrivere sulla Eprom. Il ponte RS2 invece raddrizza la tensione senza livellarla in modo da ottenere una pulsazione a 100 Hz, dovuta al raddoppiamento della frequenza di rete.

E' tuttavia possibile usare anche delle ROM (read only memory) non più cancellabili, ma è un azzardo perchè basta una svista, un errore e siete fregati.

Partiamo dalla figura 4. Sono necessarie due alimentazioni stabilizzate: una a 5 volt per gli integrati e una a 34 volt (che sarà ridotta a circa 25 volt) per scrivere sulla Eprom. Il ponte RS2 invece raddrizza la tensione senza livellarla in modo da ottenere una pulsazione a 100 Hz, dovuta al raddoppiamento della frequenza di rete.

Da tale frequenza ricaveremo (come vedremo) l'impulso positivo della durata di 50 mS da fornire al piedino 18 (CE/PGR) della Eprom.

Quando si pigia il deviatore, sul pin 6 di SN7400 compare il livello H, che consente l'ingresso della frequenza di 100 Hz; tale frequenza pilota il clock (pin 15) di SN74142 (un contatore decadico con decodifica decimale).

Quando si pigia il deviatore, sul pin 6 di SN7400 compare il livello H, che consente l'ingresso della frequenza di 100 Hz; tale frequenza pilota il clock (pin 15) di SN74142 (un contatore decadico con decodifica decimale).

Al primo impulso il pin 9 va a livello basso e pilota il primo flip-flop di SN74112, il quale commuta, facendo comparire sulla sua uscita Q il livello H, che procura l'attivazione della 7216 (pin 20, OE).

Al secondo impulso il pin 7 di SN74142 si porta a livello basso ed eccita il pin 9 di SN7400 , con conseguente passaggio del pin 8 di SN7400 a livello alto; ciò provoca l'attivazione della tensione di circa 25 V su Vpp della 2716 (pin 21).

Al terzo impulso si attiva il secondo flip-flop di SN74112, che trasmette il suo livello H su CE/PGR (pin 18 di 7216). Tale livello alto dura per 5 cicli di clock, finchè l'avanzamento del contatore, all'ottavo impulso, fa tornare a livello basso il segnale su CE/PGM, resettando il secondo flip-flop di SN74112. I cinque cicli di clock contano per 0,01 Sec ciascuno, per un totale di 50 mS

Il nono impulso, infine interrompe la tensione di 25 volt, disattiva la selezione (pin 20, OE) della Eprom, blocca l'iniezione dell'onda quadra a 100 Hz ed insomma resetta il tutto, cosichè la 2716, a fine ciclo, si troverà sempre nello stato di lettura.

Nella tabella di figura 3 (in basso, a sinistra) è rappresentata la sequenza di scrittura or ora descritta.

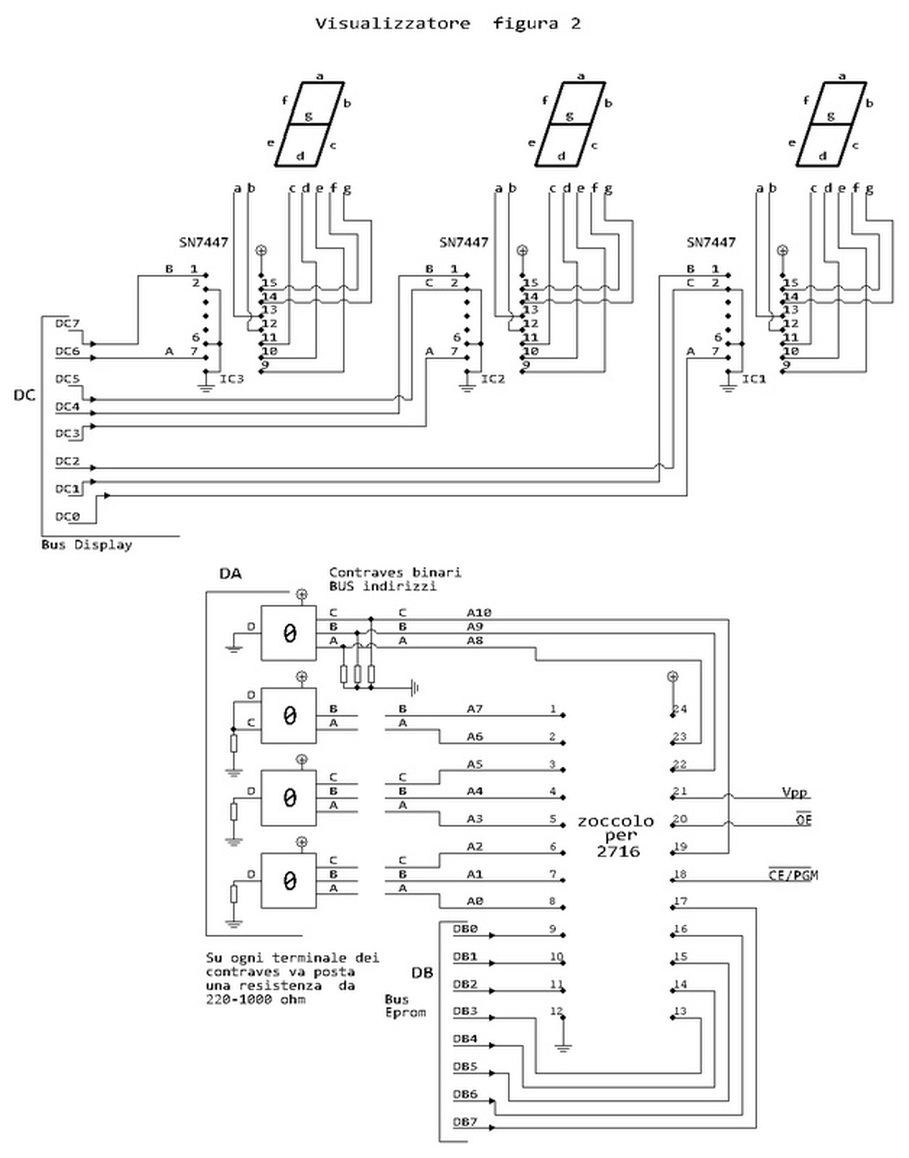

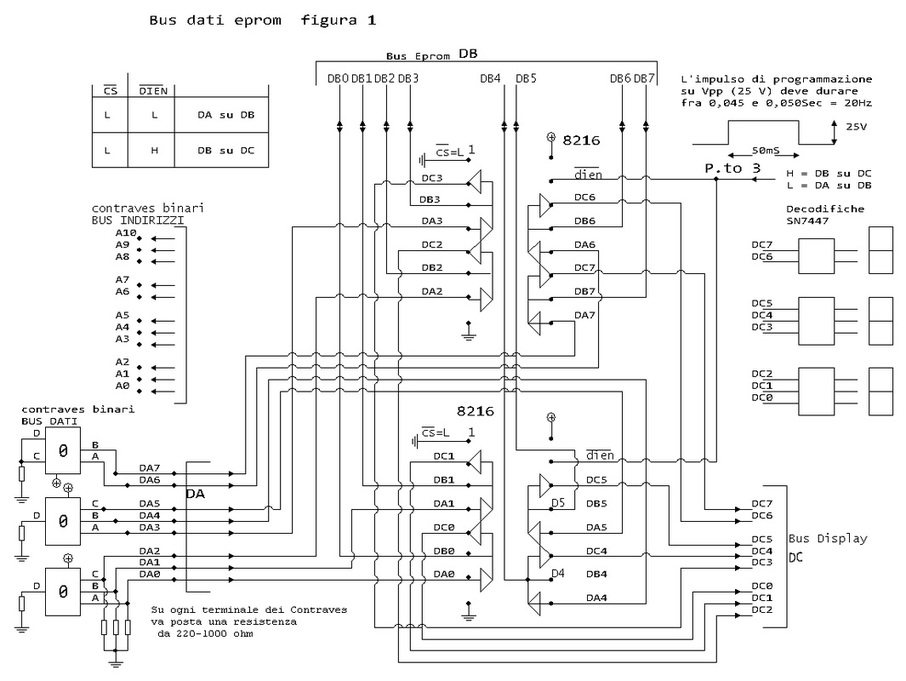

Nel prosieguo è trattato tutto il sistema di indirizzamanto della Eprom, di immissione dei byte di scrittura sul bus dati della 2716 e di visualizzazione ottale. La figura 1 mostra come i byte dai vengano presentati sul relativo bus della Eprom durante la scrittura e come i contenuti, una volta scritti, vengano visualizzati, in codice ottale su tre display a sette segmenti.

In primo luogo

Al secondo impulso il pin 7 di SN74142 si porta a livello basso ed eccita il pin 9 di SN7400 , con conseguente passaggio del pin 8 di SN7400 a livello alto; ciò provoca l'attivazione della tensione di circa 25 V su Vpp della 2716 (pin 21).

Al terzo impulso si attiva il secondo flip-flop di SN74112, che trasmette il suo livello H su CE/PGR (pin 18 di 7216). Tale livello alto dura per 5 cicli di clock, finchè l'avanzamento del contatore, all'ottavo impulso, fa tornare a livello basso il segnale su CE/PGM, resettando il secondo flip-flop di SN74112. I cinque cicli di clock contano per 0,01 Sec ciascuno, per un totale di 50 mS

Il nono impulso, infine interrompe la tensione di 25 volt, disattiva la selezione (pin 20, OE) della Eprom, blocca l'iniezione dell'onda quadra a 100 Hz ed insomma resetta il tutto, cosichè la 2716, a fine ciclo, si troverà sempre nello stato di lettura.

Nella tabella di figura 3 (in basso, a sinistra) è rappresentata la sequenza di scrittura or ora descritta.

Nel prosieguo è trattato tutto il sistema di indirizzamanto della Eprom, di immissione dei byte di scrittura sul bus dati della 2716 e di visualizzazione ottale. La figura 1 mostra come i byte dai vengano presentati sul relativo bus della Eprom durante la scrittura e come i contenuti, una volta scritti, vengano visualizzati, in codice ottale su tre display a sette segmenti.

In primo luogo

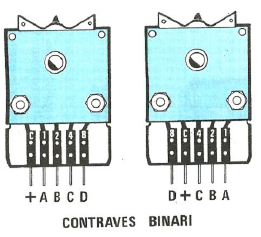

In primo luogo viene composto l'indirizzo della cella di memoria per il tramite del gruppo di quattro Contraves binari di figura 2: il bus è formato da 11 linee (da A0 ad A10). Normalmente i Contraves posseggono 4 uscite più l'alimentazione positiva, ma poiché la forma di impacchettamento ottale ha il seguente formato xx xxx xxx, non sfrutteremo tutti i contatti A, B, C D.

Su tutte le uscite porremo una resistenza da 220-1000 Ω, ma collegheremo solo quelle necessarie al tipo di formato che intendiamo usare. Inoltre normalmente i Contraves sono decimali , ma di dieci numeri sfrutteremo solo quelli dallo zero al sette o dallo zero al tre, pertanto con i primi tre conteremo da zero fino a 255, mentre con il quarto da zero fino a sette; poichè 256 x 8 fanno appunto 2048, in questo modo potremo implementare tutte le celle di memoria della Eprom 2716.

Co lo stesso sistema e con un gruppo di tre contraves implementeremo anche il bus dati (vedi figura 1)

Su tutte le uscite porremo una resistenza da 220-1000 Ω, ma collegheremo solo quelle necessarie al tipo di formato che intendiamo usare. Inoltre normalmente i Contraves sono decimali , ma di dieci numeri sfrutteremo solo quelli dallo zero al sette o dallo zero al tre, pertanto con i primi tre conteremo da zero fino a 255, mentre con il quarto da zero fino a sette; poichè 256 x 8 fanno appunto 2048, in questo modo potremo implementare tutte le celle di memoria della Eprom 2716.

Co lo stesso sistema e con un gruppo di tre contraves implementeremo anche il bus dati (vedi figura 1)

Inserendo, dopo l'accensione del marchingegno, la Eprom vuota avremo la visualizzazione sui dispay del contenuto della cella correntemente selezionata con i contraves degli indirizzi, se la Eprom sarà vuota vedremo apparire il numero 377 su qualunque cella selezioneremo con il selettore degli indirizzi.

Se volessimo inserire il byte 323 all'indirizzo 000 00 000 000, lo selezioneremo con i contraves di selezione indirizzi, scriveremo il numero voluto con i contraves del bus dati e pigeremo S1.

Ne conseguirà un ciclo così concepito:

a) Il byte sarà deviato dagli integrati 8216 sul bus dati della Eprom;

b) avverrà l'attivazione, attraverso OE del cip Eprom;

c) verrà inviata la tensione di 25 volt su Vpp;

d) il pin CE/PGM passerà da livello basso a livello alto e ancora a libello basso per un intervallo di tempo di 50 millisecondi;

e) il numero immesso comparirà sui display, sempre per mezzo degli 8216, confermandoci l'avvenuta scrittura.

Insomma gli 8216, a riposo, convogliano al display il contenuto della cella di memoria, ma durante la scrittura deviano il byte, impostato sui contraves dei dati, sul bus dati della 2716.

Se volessimo inserire il byte 323 all'indirizzo 000 00 000 000, lo selezioneremo con i contraves di selezione indirizzi, scriveremo il numero voluto con i contraves del bus dati e pigeremo S1.

Ne conseguirà un ciclo così concepito:

a) Il byte sarà deviato dagli integrati 8216 sul bus dati della Eprom;

b) avverrà l'attivazione, attraverso OE del cip Eprom;

c) verrà inviata la tensione di 25 volt su Vpp;

d) il pin CE/PGM passerà da livello basso a livello alto e ancora a libello basso per un intervallo di tempo di 50 millisecondi;

e) il numero immesso comparirà sui display, sempre per mezzo degli 8216, confermandoci l'avvenuta scrittura.

Insomma gli 8216, a riposo, convogliano al display il contenuto della cella di memoria, ma durante la scrittura deviano il byte, impostato sui contraves dei dati, sul bus dati della 2716.

Decodifica programmabile per operazioni di input output

Ciò che vi presento è una decodifica programmabile, ossia che dà la possibilità di impostare un indirizzo qualsiasi all'interno del bus di input/output o.

Nel caso specifico mi riferisco al bus indirizzi da A0 ad A7 input/output, ma nulla osta di estenderlo anche al bus di indirizzamento della memoria.

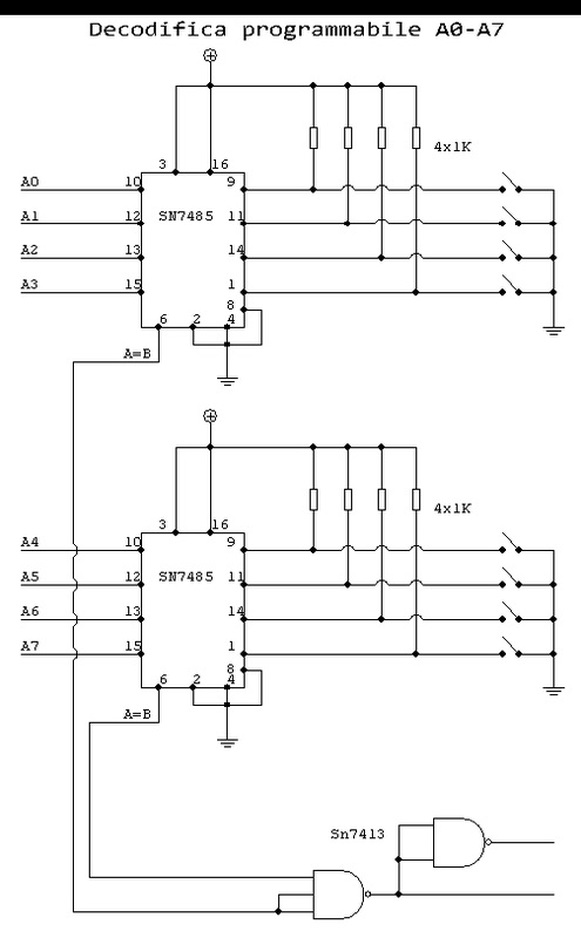

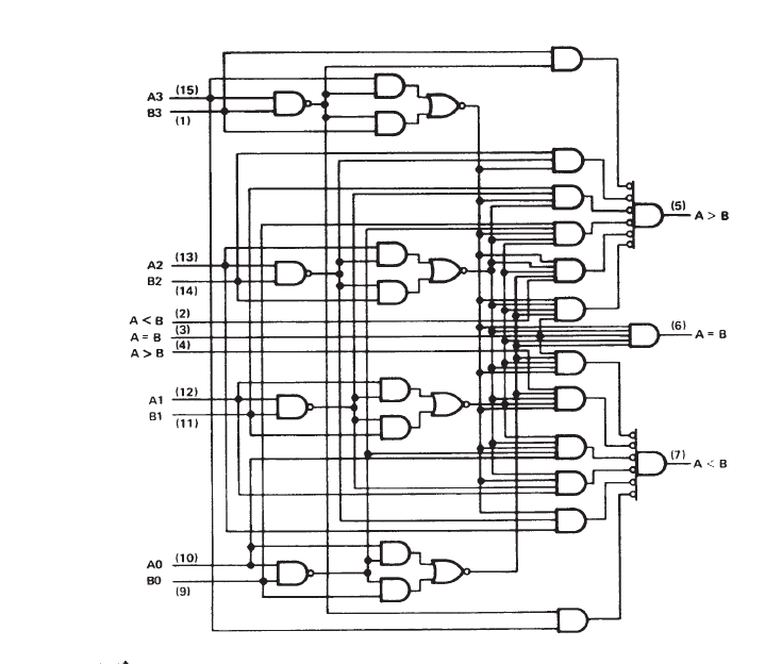

Il dispositivo è implementato da due SN7485, comparatori di grandezza a 4+4 bit, vedi figura 1.

Se i bit che vengono messi a confronto sono uguali l'uscita di verifica di uguaglianza reagisce con un livello alto. A noi interessa solo questa uscita, quindi trascureremo l'uscita di maggiore e di minore.

Nel caso specifico mi riferisco al bus indirizzi da A0 ad A7 input/output, ma nulla osta di estenderlo anche al bus di indirizzamento della memoria.

Il dispositivo è implementato da due SN7485, comparatori di grandezza a 4+4 bit, vedi figura 1.

Se i bit che vengono messi a confronto sono uguali l'uscita di verifica di uguaglianza reagisce con un livello alto. A noi interessa solo questa uscita, quindi trascureremo l'uscita di maggiore e di minore.

Con due circuiti SN7485 copriamo tutto il bus di I/O; il confronto viene fatto con degli interruttori on/off, vedi figura 1.

Se la combinazione dello stato degli interruttori eguaglia lo stato del bus indirizzi allora avremo un segnale alto sull'uscita di parità.

Lo schema è più eloquente di ogni altra spiegazione:

i bit vengono confrontati a coppie di cui un elemento appartiene al bu di I/O e l'altro elemento appartiene al gruppo degli interruttori. Per comodità il segnale può essere prelevato in maniere diretta o negata.

Se la combinazione dello stato degli interruttori eguaglia lo stato del bus indirizzi allora avremo un segnale alto sull'uscita di parità.

Lo schema è più eloquente di ogni altra spiegazione:

i bit vengono confrontati a coppie di cui un elemento appartiene al bu di I/O e l'altro elemento appartiene al gruppo degli interruttori. Per comodità il segnale può essere prelevato in maniere diretta o negata.

La selezione è di un solo indirizzo univoco alla volta, ma nulla vieta di approntare una pluralità di dispositivi.

Nel caso voleste servirvene per il bus indirizzi della memoria, saranno necessari quattro SN7485 e due porte NAND di cui una a quattro ingressi.

Naturalmente il circuito non può funzionare da solo, ma necessita del sincronismo con i segnali di I/O REQUEST e di READ o WRITE.

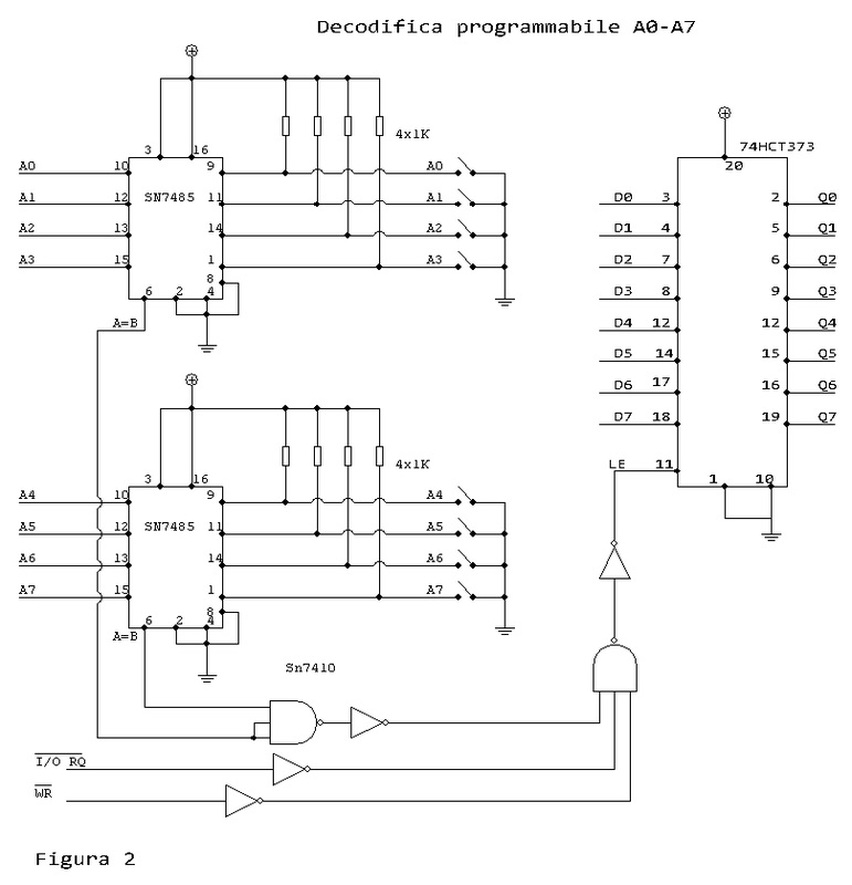

Consideriamo ora di voler emettere e mantenere un livello alto all'uscita Q7 del 74HCT373 (figura2) con indirizzo programmato #00 101 100 (054 ottale).

Intanto predisporremo gli interruttori sui due SN7485 in modo che A0, A1, A4, A6, A7 siano chiusi verso massa, in modo da riprodurre l'indirizzo #00 101 100, successivamente invieremo un byte che presenti un livello alto all'ottavo bit: 10 0000 000 = 200 ottale.

Nel caso voleste servirvene per il bus indirizzi della memoria, saranno necessari quattro SN7485 e due porte NAND di cui una a quattro ingressi.

Naturalmente il circuito non può funzionare da solo, ma necessita del sincronismo con i segnali di I/O REQUEST e di READ o WRITE.

Consideriamo ora di voler emettere e mantenere un livello alto all'uscita Q7 del 74HCT373 (figura2) con indirizzo programmato #00 101 100 (054 ottale).

Intanto predisporremo gli interruttori sui due SN7485 in modo che A0, A1, A4, A6, A7 siano chiusi verso massa, in modo da riprodurre l'indirizzo #00 101 100, successivamente invieremo un byte che presenti un livello alto all'ottavo bit: 10 0000 000 = 200 ottale.

comandi per lo Z80:

000 001 076 Carica A con <b2>

000 002 200 <b2> cioè 10 000 000

000 003 323 output <b2>

000 004 054 <b2>

000 005 166 alt

Osserveremo che l'uscita Q7 (figura 2) si porterà stabilmente a livello alto, mentre tutte le altre saranno stabili a livello basso.

I codici corrispondenti al livello alto per ciascuna uscita, adoperata singolarmente, sono

Q0: 00 000 001 = 001 ottale

Q1: 00 000 010 = 002

Q2: 00 000 100 = 004

Q3: 00 001 000 = 010

Q4: 00 010 000 = 020

Q5: 00 100 000 = 040

Q6: 01 000 000 = 100

Q7: 10 000 000 = 200

Per disattivare l'uscita, or ora impostata, dovremo caricare l'accumulatore con il byte 000 e inviare all'indirizzo #00 101 100 = 054 ottale

E' naturale che le uscite del 74HCT370 possono essere pilotate simultaneamente attraverso l'invio di un byte dedicato.

Inviando, ad esempio, il byte 123 ottale, ossia 01 010 011, attiveremo Q0, Q1, Q4, Q6 (74HCT370), lasciando le altre uscite inattive (livello zero). Invece il byte 11 010 010 attiva Q7 , disattiva Q0 e lascia il resto inalterato.

Un circuito a transistor asservito ad ogni singola uscita potrà pilotare un relè o qualsiasi altro attuatore.

Naturalmente dovrete posizionare questa decodifica programmabile al di fuori di ogni altro segmento già in uso.

000 001 076 Carica A con <b2>

000 002 200 <b2> cioè 10 000 000

000 003 323 output <b2>

000 004 054 <b2>

000 005 166 alt

Osserveremo che l'uscita Q7 (figura 2) si porterà stabilmente a livello alto, mentre tutte le altre saranno stabili a livello basso.

I codici corrispondenti al livello alto per ciascuna uscita, adoperata singolarmente, sono

Q0: 00 000 001 = 001 ottale

Q1: 00 000 010 = 002

Q2: 00 000 100 = 004

Q3: 00 001 000 = 010

Q4: 00 010 000 = 020

Q5: 00 100 000 = 040

Q6: 01 000 000 = 100

Q7: 10 000 000 = 200

Per disattivare l'uscita, or ora impostata, dovremo caricare l'accumulatore con il byte 000 e inviare all'indirizzo #00 101 100 = 054 ottale

E' naturale che le uscite del 74HCT370 possono essere pilotate simultaneamente attraverso l'invio di un byte dedicato.

Inviando, ad esempio, il byte 123 ottale, ossia 01 010 011, attiveremo Q0, Q1, Q4, Q6 (74HCT370), lasciando le altre uscite inattive (livello zero). Invece il byte 11 010 010 attiva Q7 , disattiva Q0 e lascia il resto inalterato.

Un circuito a transistor asservito ad ogni singola uscita potrà pilotare un relè o qualsiasi altro attuatore.

Naturalmente dovrete posizionare questa decodifica programmabile al di fuori di ogni altro segmento già in uso.

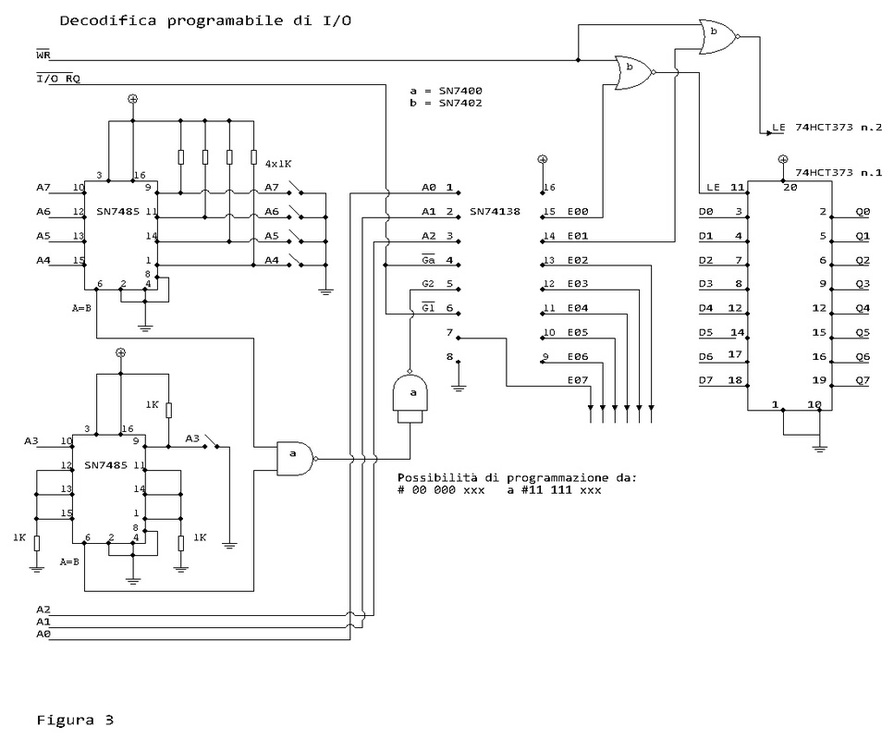

E' chiaro che se vi servissero un gruppo di indirizzi adiacenti, ad esempio, per pilotare la selezione di otto porte diverse, lascerete liberi A0, A1, A2 per governare una decodifica binaria a tre bit a otto uscite (demultiplexer), del tipo SN74138, come mostrato nello schema di figura 3. Per memorizzare stabilmente lo stato transitorio di scrittura servirà un circuito di otto flip-flop di tipo D, un 74HCT373.

Le otto porte, selezionabili da #000 a #111 (da 0 a 7 ottale), potranno essere spostate, a piacere, in un qualsiasi punto del bus indirizzi di I/O compreso tra #00 000 xxx e #11 111 xxx (tra 00x e 37x ottale) ottale, in sola scrittura.

A0, A1, A2 assumono (SN74138) la seguente configurazione:

000 = E00, 001 = E01, 010 = E02, 010 = E03, 100 = E04, 101 = E05, 110 = E06, 111 =E07.

Ad ogni uscita di SN74138 potrà essere associato un 74HCT373 (figura 3) per un totale di 64 uscite di pilotaggio dispositivo; il bus dati del microprocessore deve essere collegato agli ingressi di 74HCT737 da D0 a D7.

Esempio:

vogliamo attivare la porta che governa il 74HCT373 numero 6, programmato all'indirizzo I/O #01 100 110 e portare a livello alto le sue uscite Q0, Q3,Q5,Q7 = 10 101 001 (251 ottale)

Gli interruttori sui due SN7485 verranno così predisposti A0, A3,A4 A7 a massa = #01 100 110 (146 ottale).

000 000 076 Carica l'accumulatore A con il byte <b2>

000 001 251 <b2> cioè 10 101 001

000 002 323 out <b2>

000 003 146 <b2>

000 004 166 alt

Le otto porte, selezionabili da #000 a #111 (da 0 a 7 ottale), potranno essere spostate, a piacere, in un qualsiasi punto del bus indirizzi di I/O compreso tra #00 000 xxx e #11 111 xxx (tra 00x e 37x ottale) ottale, in sola scrittura.

A0, A1, A2 assumono (SN74138) la seguente configurazione:

000 = E00, 001 = E01, 010 = E02, 010 = E03, 100 = E04, 101 = E05, 110 = E06, 111 =E07.

Ad ogni uscita di SN74138 potrà essere associato un 74HCT373 (figura 3) per un totale di 64 uscite di pilotaggio dispositivo; il bus dati del microprocessore deve essere collegato agli ingressi di 74HCT737 da D0 a D7.

Esempio:

vogliamo attivare la porta che governa il 74HCT373 numero 6, programmato all'indirizzo I/O #01 100 110 e portare a livello alto le sue uscite Q0, Q3,Q5,Q7 = 10 101 001 (251 ottale)

Gli interruttori sui due SN7485 verranno così predisposti A0, A3,A4 A7 a massa = #01 100 110 (146 ottale).

000 000 076 Carica l'accumulatore A con il byte <b2>

000 001 251 <b2> cioè 10 101 001

000 002 323 out <b2>

000 003 146 <b2>

000 004 166 alt

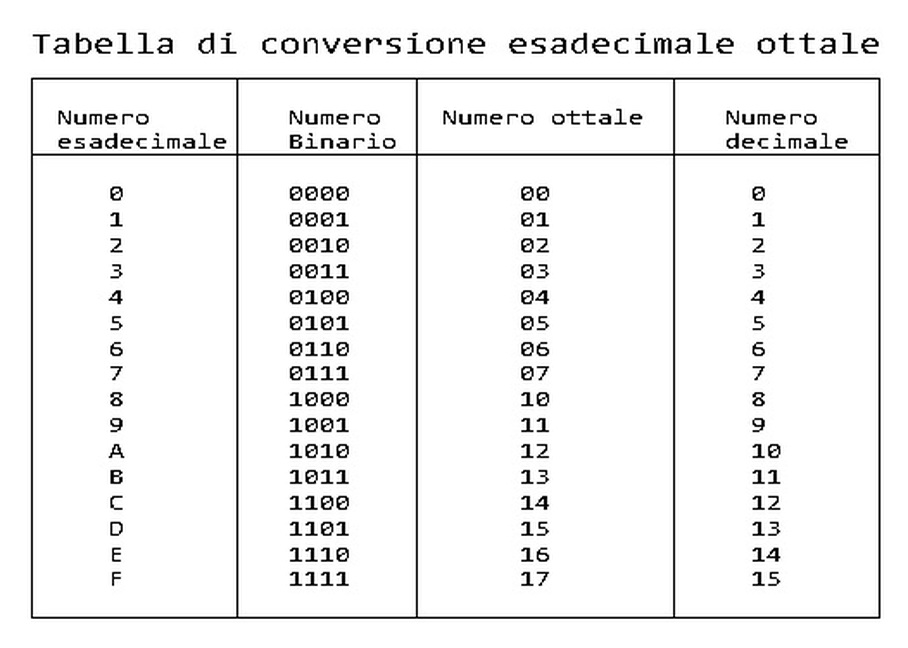

Il Byte converto in esadecomale viene diviso in due parti di quattro bit ossia: xxxxxxxx = xxxx xxxx, per altro nel sitema di numerazione ottale lo stesso Byte viene diviso in tre parti : una di due bit e due di tre bit xxxxxxxx = xx xxx xxx.

Nell'esadecimale il gruppo di quattro bit conta da 0 ad F, nel sistema ottale i due gruppi da tre bit contano da 0 a 7, mentre il gruppo di due bit conta da 0 a tre.

Pertanto il numero binario 11111111 in esadecimale è così interpretato: 1111 1111 = FF; in ottale lo stesso numero invece è tradotto così 11 111 111 = 377.

Nell'esadecimale il gruppo di quattro bit conta da 0 ad F, nel sistema ottale i due gruppi da tre bit contano da 0 a 7, mentre il gruppo di due bit conta da 0 a tre.

Pertanto il numero binario 11111111 in esadecimale è così interpretato: 1111 1111 = FF; in ottale lo stesso numero invece è tradotto così 11 111 111 = 377.

|

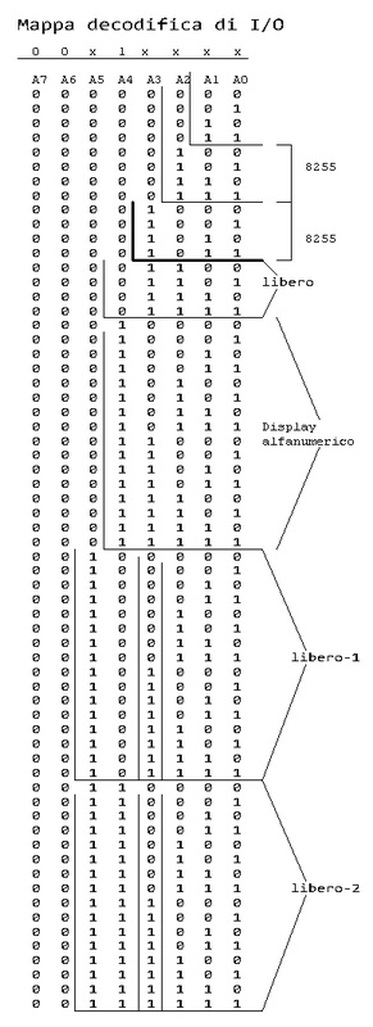

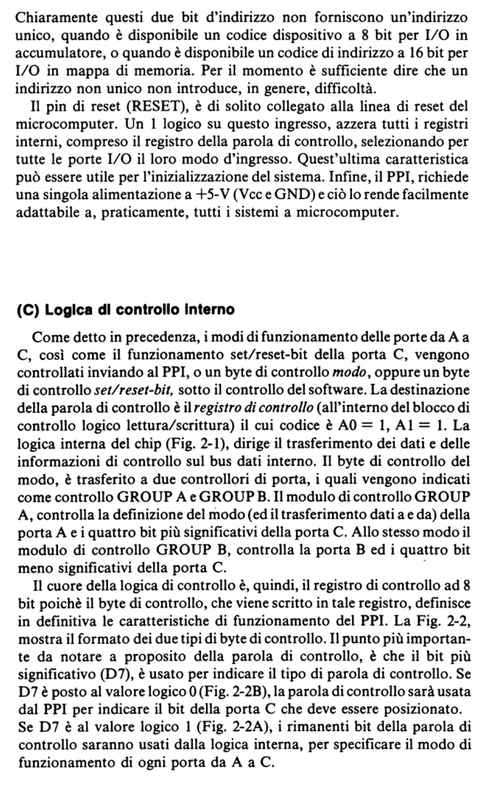

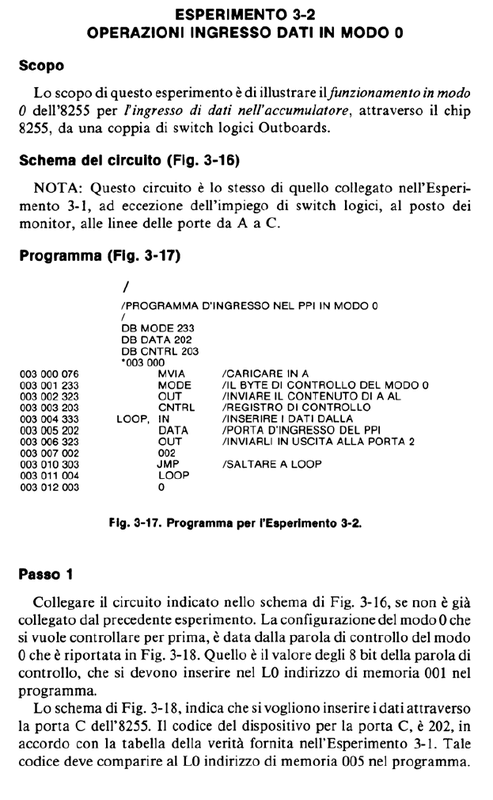

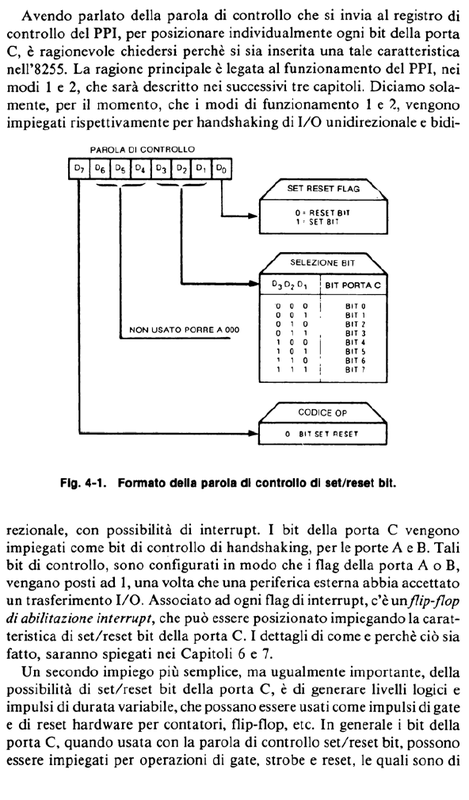

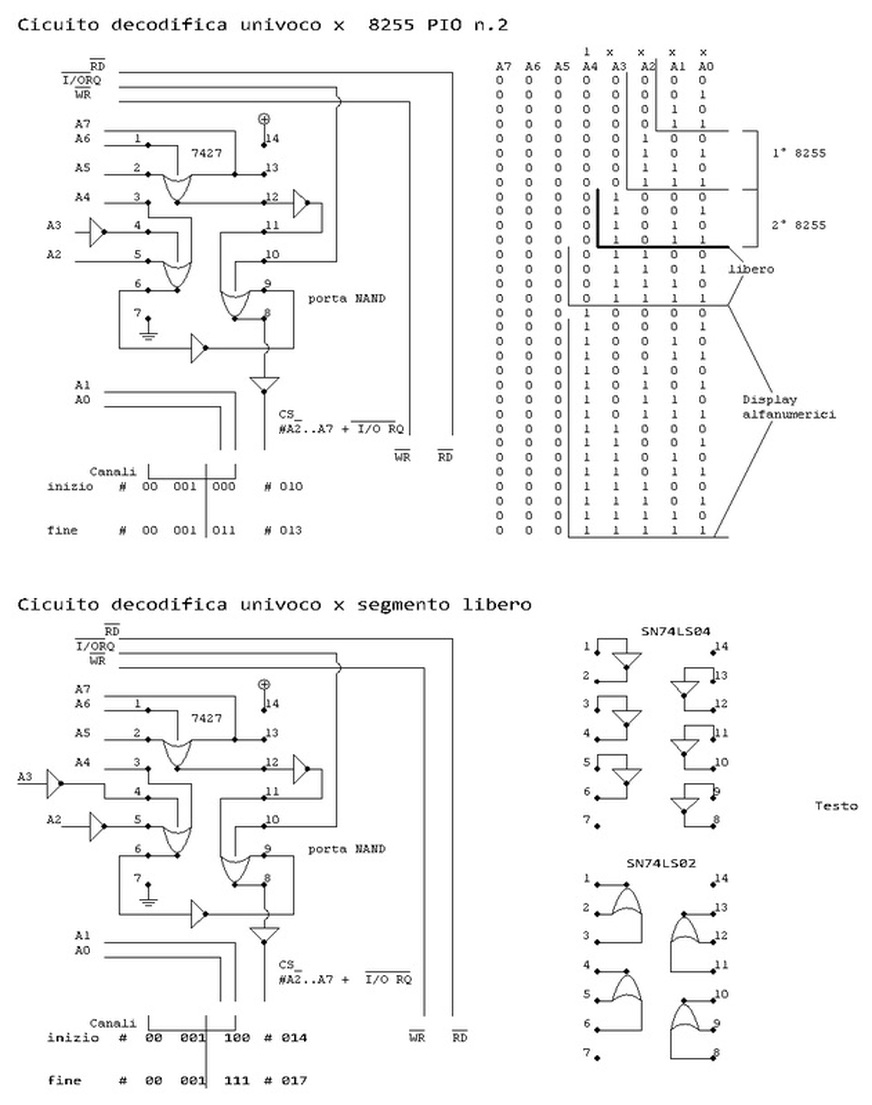

Nella figura a lato viene riportata la mappa delle operazioni di ngresso/uscita (I/O) che presenterò nel prosieguo della trattazione.

Da 000 ad 003 viene servita la tastiera e il visualizzatore, come già descritto; da 004 a 007 viene indirizzata una prima PIO 8255 di cui vi parlerò in seguito; da 010 ad 013 è possibile aggiungere una seconda PIO 8255 oppure una UART; da 014 a 017 è posizionato il segmento libero n. 0; da 020 a 037 verrà indirizzato un visualizzatore alfanumerico a 16 caratteri, di cui vi parlerò; da 040 a 057 è posizionato un secondo segmento libero di 16 indirizzi chiamato libero n. 1, ache su questo segmento verrà collegato un sistema di porte di comunicazione, per operazioni di uscita su attuatori.; da 060 a 077 viene decodificato un altro segmento, chiamato libero n. 2, con funzioni uguali al precedente. Naturalmente nulla osta che voi modifichiate la destinazione di questa mappa, a seconda delle vostre esigenze, con ulteriore decodifica dei singoli segmenti.. Non vado oltre perchè già così viene data la possibilità di 64 indirizzi, da cui potrete ricavare, come vi mostrerò, un numero molto più alto di possibilità di comunicazione in uscita ed in ingresso. Non mancherà la descrizione, anche se piuttosto complessa, di un sistema di conversione analogico-digitale, ripetibile per quante volte vi può servire. Tale conversione in componenti discreti potrebbe essere supplita da un unico circuito integrato DAC, ad esempio AD7522, ma dubito che oramai sia reperibile. Resterà infine l'implementazione del sistema di interrupt, e la regolazione della loro priorità. Per quanto riguarda il software, vi fornitò un certo numero di programmi eseguibili, in linguaggio macchina, da questa emulazione di "Arduino". Il divertimento per chi è già appassionato o si appasionerà è assicurato. |

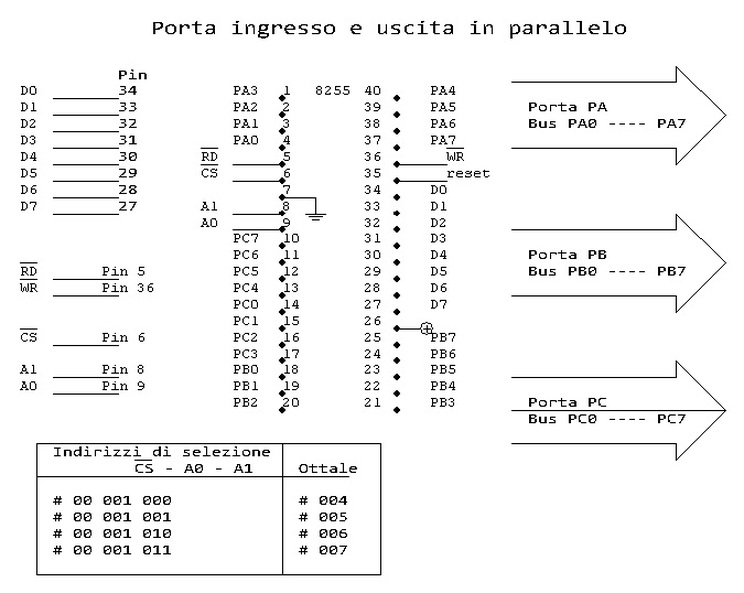

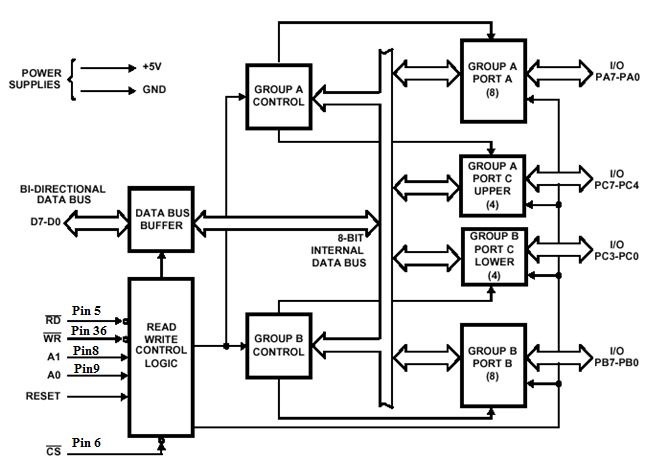

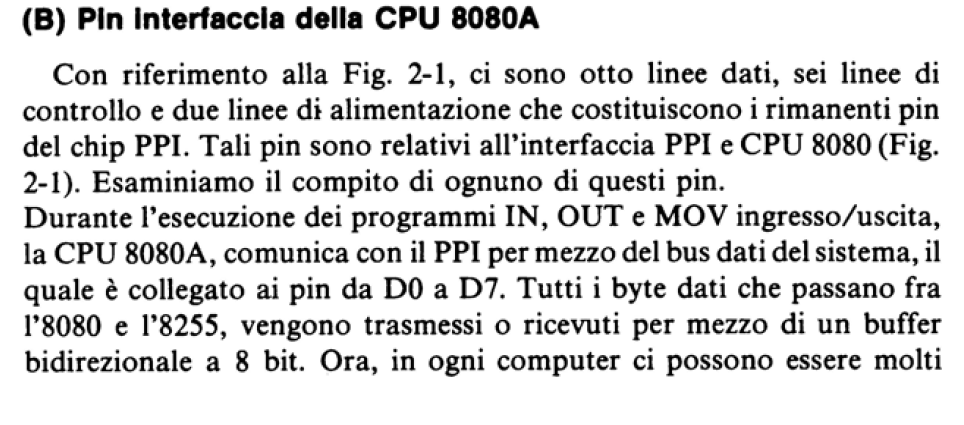

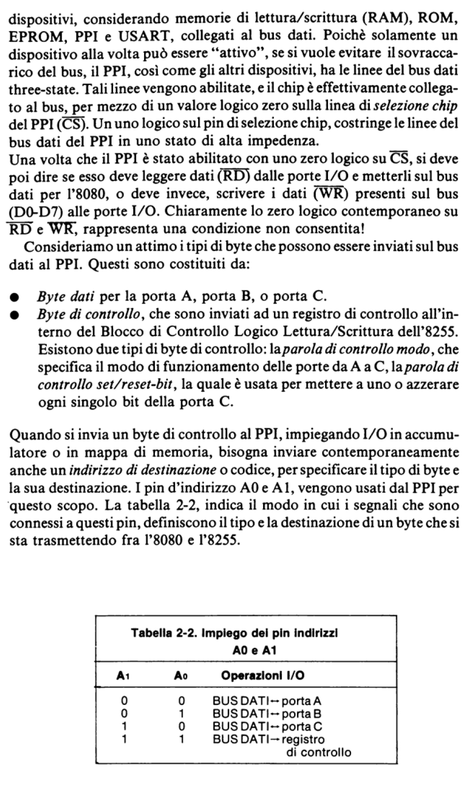

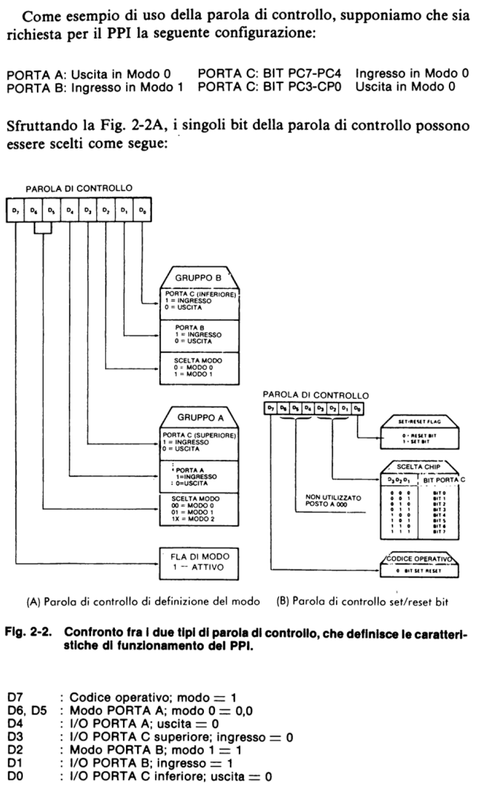

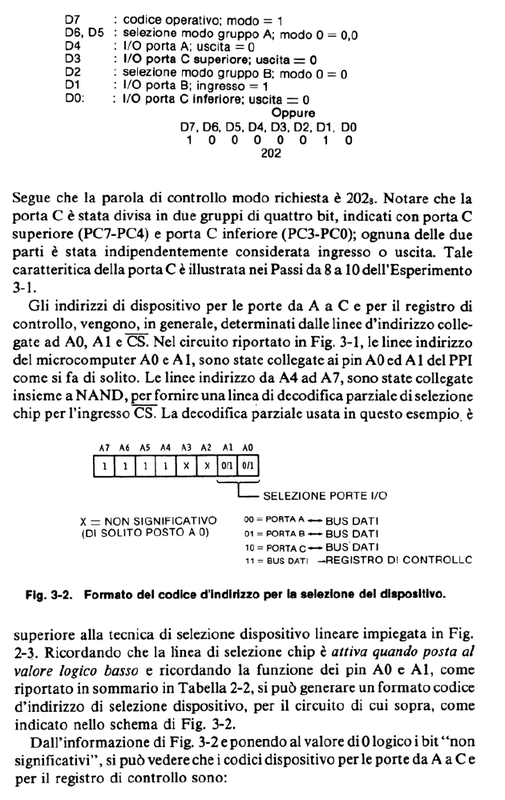

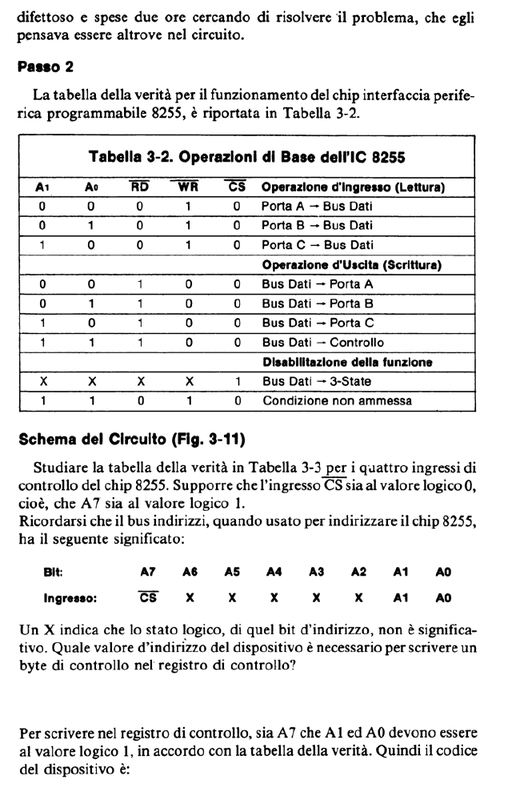

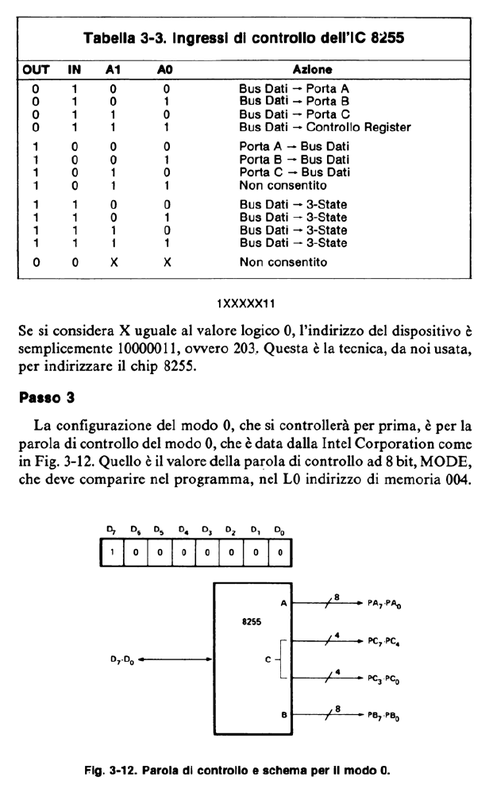

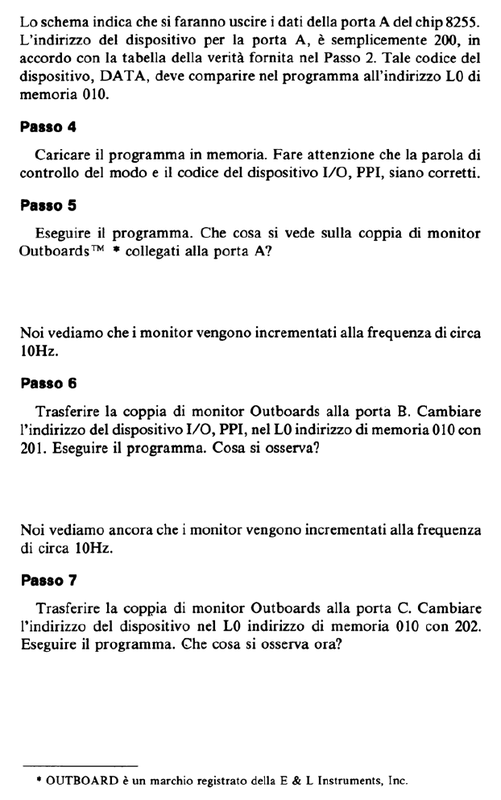

Operazioni di ingresso / uscita con PIO 8255 n.1

Nella figura più in alto c'è lo schema di collegamento del cip 8255. Questo integrato era nato per l'8080, ma funziona perfettamente anche con lo Z80 e mette a disposizione tre porte di I/O programmabili cliccando sui seguenti pdf potrete scaricare una sorta di manuale di funzionamento dell'8255.

Io, per il momento, mi limito a fornirvi lo schema di collegamento alla CPU e le spiegazioni per l'uso.

La decodifica, secondo la mappa di I/O, è già stata presentata allo schema 6

Il reset viene collagato al reset della CPU.

Io, per il momento, mi limito a fornirvi lo schema di collegamento alla CPU e le spiegazioni per l'uso.

La decodifica, secondo la mappa di I/O, è già stata presentata allo schema 6

Il reset viene collagato al reset della CPU.

|

| ||||||||||||

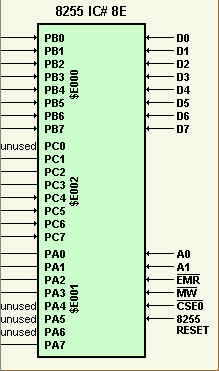

Ritenendo di non aver trascurato nulla di importante circa la PIO 8255, procederò con da implementazione di una seconda PIO sempre 8255., secondo la mappa di decodificas I/O. In più mostrerò anche la decodifica del segmento chiamato, nella stessa mappa, libero, in gradio di implementare altre quattro porte..

E' evidente la dovizia di schemi accessori, ce ne sono anche per i beati. Voi sfronderete il troppo ed il vano, servendovi di quanto è nei vostri scopi.

Il modello base consigliato, a questo punto, è: CPU + 2 KB Eprom + 4Kb RAM + tastierino + visualizzatore ottale + n.2 PIO 8255. Mi raccomando servitevi dei buffers per non sovraccaricare il microprocessore.

Il modello base consigliato, a questo punto, è: CPU + 2 KB Eprom + 4Kb RAM + tastierino + visualizzatore ottale + n.2 PIO 8255. Mi raccomando servitevi dei buffers per non sovraccaricare il microprocessore.

pubblicazione iniziata l' 1/03/2016

Continua

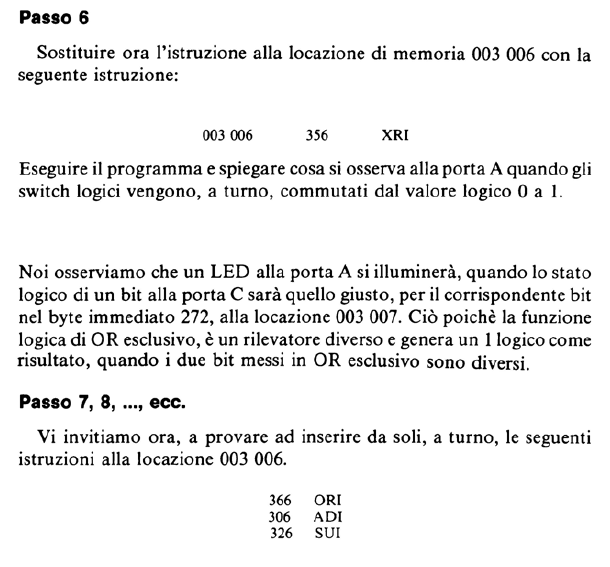

Continua